# Methodology Appnote

### **Abstract**

The goal of the Rapid Prototyping of Application-Specific Signal Processors (RASSP) program is to improve by (at least) a factor of four the time required to conceptualize, design/upgrade, and field signal processor systems. Similar improvements in design quality and life-cycle cost were also expected. The overall RASSP methodology is based upon two major beliefs:

- that concurrent design practices, using an integrated approach to hierarchical design verification, are required to improve design quality and performance

- that dramatic (>4X) decreases in cycle time can only be achieved by maximizing reuse of both hardware and software elements.

These two beliefs lead to the notion of design using modular hardware and software functions that are represented in a reuse library. To significantly improve the cycle time and cost of developing signal processing systems, major changes are required in the traditional process. RASSP innovations in the areas of processor architecture selection and verification using Virtual Prototyping and software development using graphical design methods and autocoding have demonstrated the largest contributions to the 4X goals.

In addition to speeding up the individual processes, RASSP reduced a portion of the cycle time by eliminating time-consuming and costly design rework cycles. The RASSP process provides a method to support high-quality designs that lead to first-pass success of all hardware and software elements.

## **Purpose**

This application note serves as the gateway to the other application notes that detail the RASSP developed technologies as well as the case studies that document the actual use of the methodolgy and technologies to specific projects. The following provides a generic description of the process to follow in order to achieve the RASSP benefits. It does not get into the use of the particular tools nor does it provide examples for how to perform designs. These are provided in the Case Studies and Application Notes. By adopting and following the processes described in this document a program will be able to realize the same productivity improvements that Lockheed Martin Advanced Technology Laboratories have demonstrated on the RASSP program.

## Roadmap

- 1.0 Executive Summary

- 1.1 RASSP Methodology Design Process

- 2.0 Introduction

- 2.1 Objective of this Application Note

- 2.2 Organization of the Application Note

- 2.3 Linkage to other Application Notes

- 3.0 IDEF Representation of WorkflowsProcess

- 3.1 What is a Workflow

- 3.2 Activity Definitions

- 3.3 Workflow Capture

- o 3.3.1 IDEF3X Overview

- o 3.3.2 Precedence Links

- 3.4 Modeling Example

- 3.5 Summary

#### 4.0 Unifying Processes and Roles in RASSP

- 4.1 Iterative Hierarchical Virtual Prototype Process driven by Risk (Spiral Model)

- 4.2 Role of Hardware/Software Codesign

- 4.3 Role of Model Year Architecture

- 4.4 Role of Performance Modeling/Virtual Prototyping

- 4.5 Role of Design For Testability

#### 5.0 Process

- 5.1 Overview

- 5.2 Model Year Architecture

- 5.3 Systems Design Process Overview

- 5.4 Architecture Design Process Overview

- 5.5 Detailed Design Process Overview

#### 6.0 System Design Process Detailed Discussion

- 6.1 System Requirements Analysis

- o 6.1.1 System Requirements Development

- o 6.1.2 System Specification Generation

- o 6.1.3 System Requirements Review

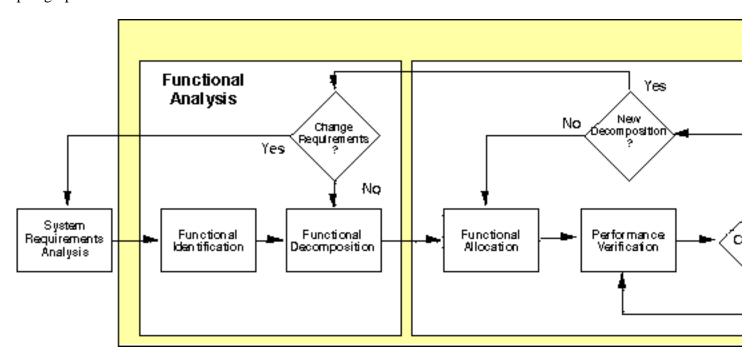

- 6.2 System Design Functional Analysis

- o 6.2.1 Functional Identification

- o 6.2.2 Functional Decomposition

- o 6.2.3 Informal Functional Analysis Design Review

- 6.3 System Partitioning

- o 6.3.1 Functional Allocation

- o 6.3.2 Performance Verification

- o 6.3.3 System Design Review

- 6.4 Other Considerations in the System Design Phase

- o 6.4.1 Use of VHDL in System Design Process

- o 6.4.2 Design for Test Tasks in System Design

- o 6.4.3 Role of the Product Development Team in System Design

- o 6.4.4 Design Reviews it System Design Process

#### 7.0 Architecture Design Process Detailed Discussion

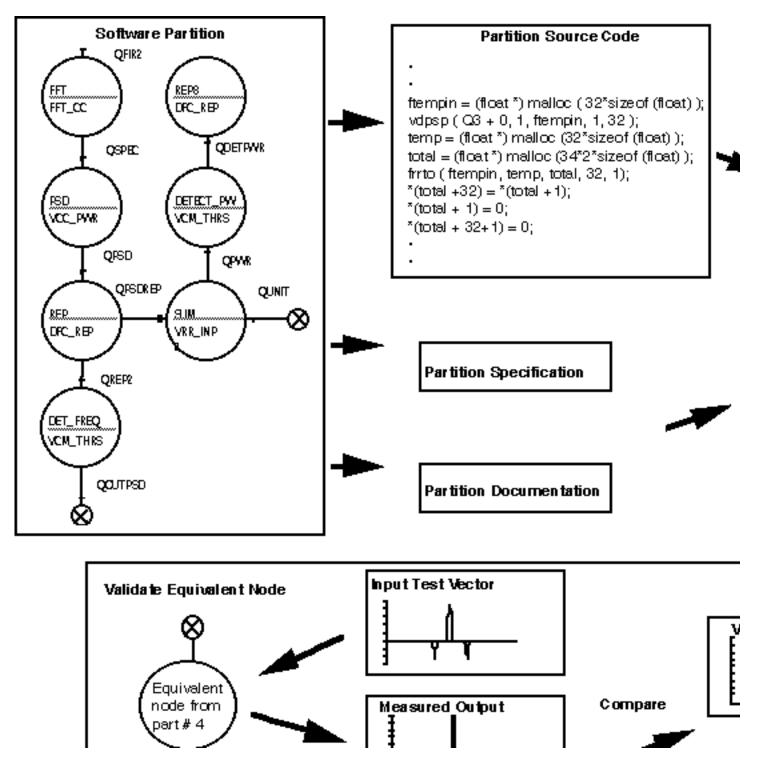

- 7.1 Functional Design o 7.1.1Architecture Sizing o 7.1.2 Selection Criteria Definition o 7.1.3 Define Non-DFG/CFG Software Tasks o 7.1.4 Flow Graph Generation o 7.1.5 Command Program Development o 7.1.6 Functional Simulation • 7.2 Architecture Selection o 7.2.1 Architecture Definition o 7.2.2 Architecture Model Synthesis o 7.2.3 Performance Simulation o 7.2.4 Implementation Analysis o 7.2.5 Trade-off Analysis • 7.3 Architecture Verification o 7.3.1 Autocode Generation o 7.3.2 Performance Simulation o 7.3.3 Refine Physical Decomposition o 7.3.4 Refine Implementation Analysis o 7.3.5 Model Availability o 7.3.6 Verification Approach Definition o 7.3.7 Simulation Development o 7.3.8 Simulation o 7.3.9 Trade-off Analysis Update • 7.4 Software in Architecture Design Process o 7.4.1Domain Primitive o 7.4.2 Domain-Primitive Graph o 7.4.3 Allocated Graph o 7.4.4 Partitioned Software Graph

- o 7.4.5 Partition Graph

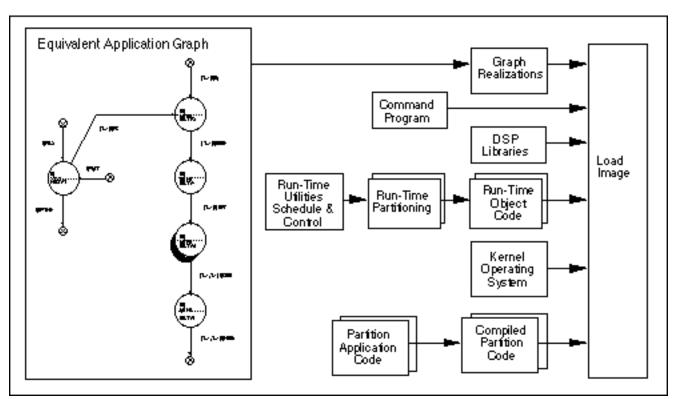

- o 7.4.6 Equivalent Application Graph

- o 7.4.7 Command Program

- o 7.4.8 DFG/Command Program Functional Simulation

- o 7.4.9 Non-DFG Software

- 7.5 Other considerations in the Architecture Design Process

- o 7.5.1Use of VHDL in Architecture Process

- o 7.5.2 Design-for-Test Tasks in Architecture Design

- o 7.5.3 Role of PDT in Architecture Process

- o 7.5.4 Design Reviews in Architecture Process

#### 8.0 Detailed Design Process Detailed Discussion

- 8.1 Module/MCM Design Process

- o 8.1.1 Module Preliminary Design

- 8.1.1.1 Develop Module Behavioral Model

- □ 8.1.1.2 Generate Module Test Plan

- □ 8.1.1.3 Perform Behavioral Funtional Simulation

- □ 8.1.1.4 Generate Module Functional Test Vectors

- □ 8.1.1.5 Generate ASIC/FPGA Requirements

- □ 8.1.1.6 Search Design Reuse

- □ 8.1.1.7 Interactive Logic Design

- □ 8.1.1.8 Preliminary Layout (Parts Placement)

- **8.1.1.9**

- □ 8.1.1.10 Perform Power/Loading Analysis

- □ 8.1.1.11 Perform Functional Timing Simulation

- □ 8.1.1.12 Select Parts

```

□ 8.1.1.14 Perform Thermal Analysis

□ 8.1.1.15 Perform Fault Simulation

□ 8.1.1.16 Generate Module Preliminary Design Document

□ 8.1.1.17 Conduct Preliminary Module Design Review

o 8.1.2 Module Final Design

□ 8.1.2.1 Module Place and Route

□ 8.1.2.2 Udate Module Preliminary Design Document

□ 8.1.2.3 Perform Final Design Functional Timing Simulation

□ 8.1.2.4 Perform Final Design Thermal Analysis

□ 8.1.2.5 Perform Final Design Critical Path Analysis

□ 8.1.2.6 Perform Production Timing Simulation

□ 8.1.2.7 Generate Module Test Procedure and ATE Test Vectors

□ 8.1.2.8 Design and Build Test Adapters

□ 8.1.2.9 Generate Module Artwork and Manufacturing Tools

□ 8.1.2.10 Prepare Module Release Package

■ 8.1.2.11 Conduct Pre-Release Design Review

o 8.1.3 Hardware Fabrication, Assembly, and Unit Test

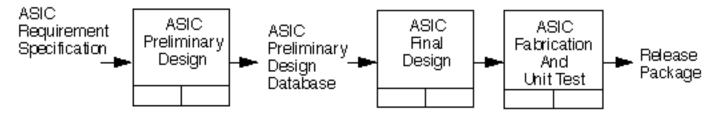

• 8.2 ASIC Design Process

o 8.2.1 ASIC Preliminary Design

o 8.2.2 ASIC Final Design

o 8.2.3 ASIC Fabrication and Unit Test

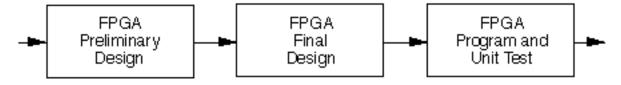

• 8.3 FPGA Design Process

o 8.3.1 FPGA Preliminary Design

o 8.3.2 FPGA Final Design

o 8.3.3 FPGA - Program Device and Unit Test

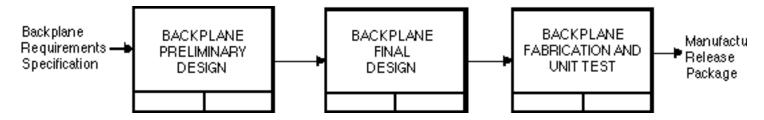

• 8.4 Backplane Design Process

o 8.4.1 Backplane Preliminary Design

o 8.4.2 Backplane Final Design

o 8.4.3Fabricate, Assemble, and Unit Test Phase

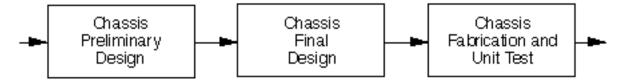

• 8.5 Chassis Design Process

o 8.5.1 Chassis Preliminary Design

o 8.5.2 Chassis Final Design

o 8.5.3 Chassis Fabrication, Assembly, and Unit Test

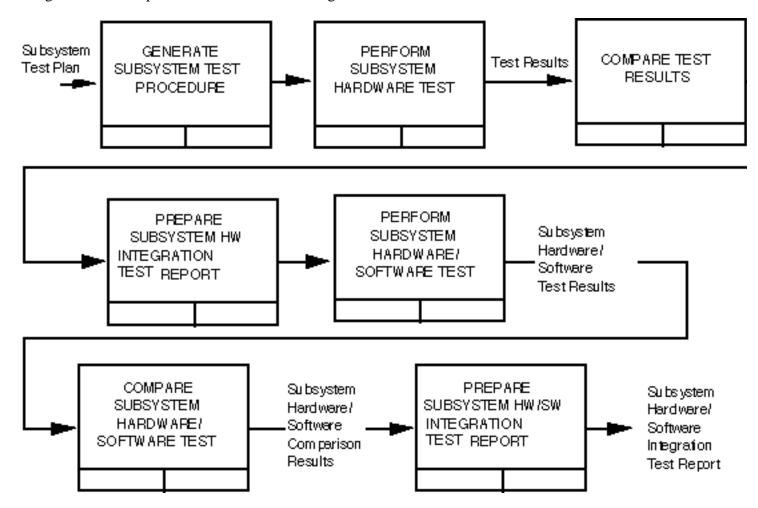

• 8.6 Subsystem Integration and Test Process

o 8.6.1 Generate Subsystem Integration Plan

o 8.6.2 Generate Subsystem Test Plan

o 8.6.3 Generate Multichassis Test Plan

o 8.6.4 Generate Chassis Test Plan

o 8.6.5 Generate Test Procedures for Each Plan

o 8.6.6 Conduct Test Procedure Review

o 8.6.7 Integrate Backplanes and Test

o 8.6.8 Integrate Chassis and Test

o 8.6.9 Integrate Subsystem and Test

• 8.7 Other Consideration in Detailed Design

o 8.7.1 Use of VHDL in the Hardware Design Task

o 8.7.2 Design For Test Tasks in Detailed Design

```

□ 8.1.1.13 Generate Production Test Vectors

#### 9.0 Integrated Software View

- 9.1 Software in the Design Process

- 9.2 Hardware/Software Codesign

- 9.3 Library Management

• 9.4 Documentation

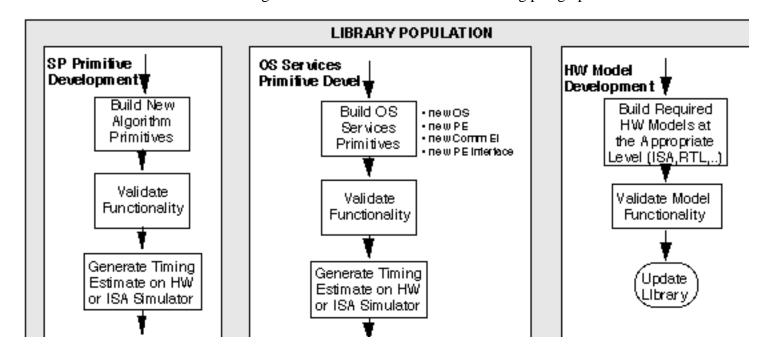

### 10.0 Library Population for Reuse

- 10.1 Signal Processing Primitive Development

- 10.2 Operating System Services Primitive Development

- 10.3 Hardware Model Development

## 11.0 References

Approved for Public Release; Distribution Unlimited Dennis Basara

Next: 2 Introduction Up: Appnotes Index Previous: Appnote Methodology Index

# RASSP Methodology Application Note

## 1.0 Executive Summary

## 1.1 RASSP Methodology Design Process

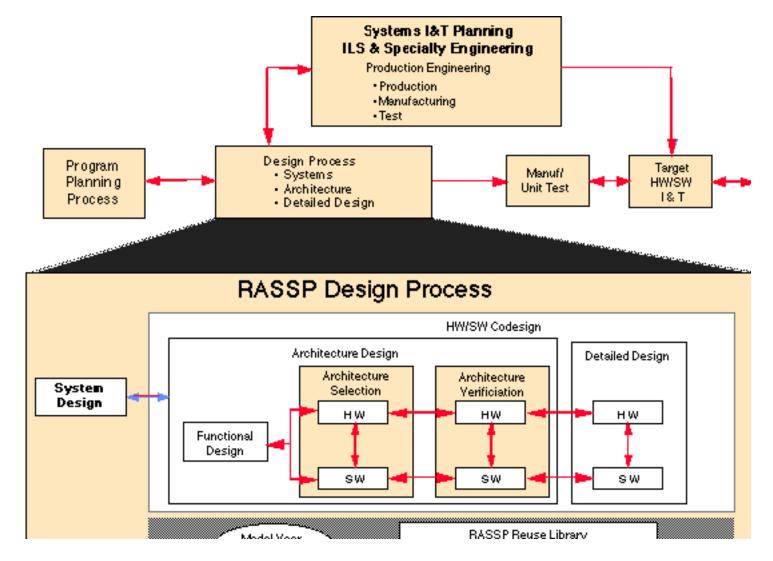

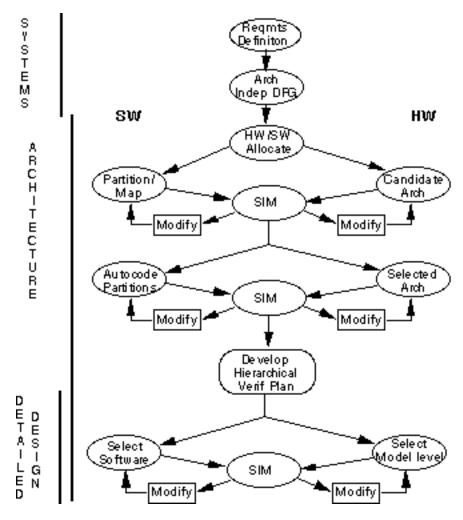

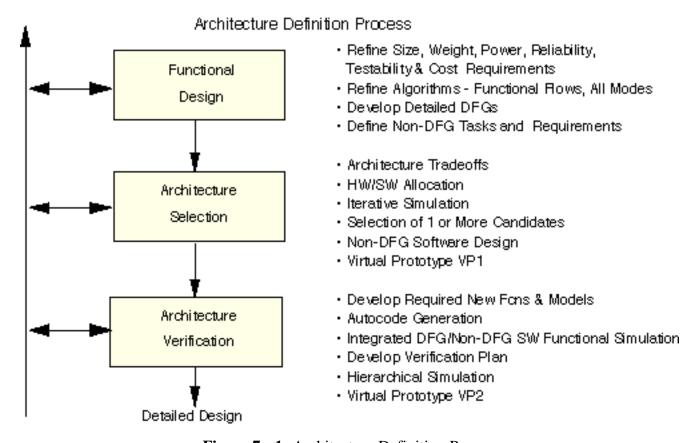

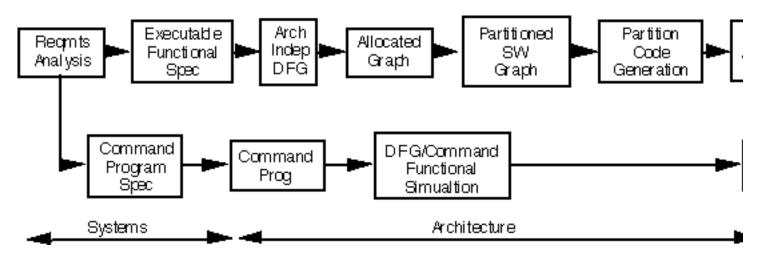

The RASSP design process has three major functional processes - the systems, architecture, and detailed design processes. It is shown in expanded form in Figure 1 - 1. The process is partitioned as a function of the abstraction level of the evolving design, not as a function of the discipline. This is the result of merging hardware and software into a true codesign process; any distinctions between hardware and software are made within the specific process. Hardware/software codesign is implemented from the initial partitioning of functions to hardware and software elements all the way to manufacturing release. At each step in the hierarchy, interactive simulation using hardware and software models is performed at equivalent levels of abstraction to verify both functionality and performance. This means that each process area is closely tied to the RASSP vision of an iterative (spiral-like) development, resulting in a series of virtual prototypes and data packages.

Figure 1 - 1: RASSP Design Process

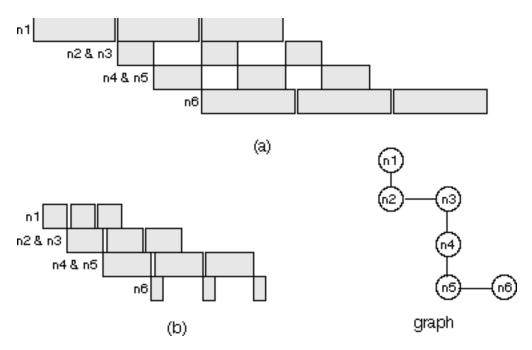

Each major cycle of the spiral process represents an iteration of a virtual prototype. Within each prototype iteration, pieces of the design can and most likely will be at different levels of maturity, as shown in Figure 4 - 1. Each piece of the design may be represented by a mini-spiral where the spiral cycles correspond to virtual prototypes of the piece. Consequently, for each major spiral cycle, there may be activity in the system, architecture, and detailed design processes.

The overall RASSP development process, shown in Figure 1 - 1, has four major elements:

- Project planning/Management Project planning/management provides the first step of the process: Develop the technical plan, and form the PDT (product development team) and the overall management approach for the specific signal processor development.

- Design Process The design process represents development of the signal processor design from requirements capture through release to manufacturing. Is has three major processes: Systems design, architecture design, and detailed design. This process takes customer requirements and results in a fully verified (functionality and performance) virtual prototype of the signal processor.

- Systems Design Process This process captures customer requirements and converts these system-level needs into processing requirements (functional and performance). Functional and performance analyses are performed to properly decompose the system-level description. The system process has only a very preliminary notion of either hardware versus software functionality or processor implementation.

- Architecture Design Process The architecture process transforms processing requirements into a candidate architecture of hardware and software elements. Architecture selection initiates the trade-offs between the different processor architecture alternatives. During this process, the system-level processing requirements are allocated to hardware and/or software functions. The hardware and software functions are verified with each other via 'co-verification" at all steps. The architecture verification process results in a detailed behavioral description of the processor hardware and the definition of the software required for each processor in the system. The intent is to verify all the code during this portion of the design, ensuring hardware/software interoperability early in the design process.

- Detailed Design As with the prior processes, the design is completed and verified for both hardware and software via a set of detailed functional and performance simulations. When this process is complete, the design is established, resulting in a fully verified virtual prototype of the system.

During the hardware portion of the detailed design process, behavioral specifications of the processor are transformed into detailed designs (RTL, and/or logic-level) through a combination of hardware partitioning, parts selection, and synthesis. Detailed designs are functionally verified using integrated simulators, and performance/timing is also verified to ensure proper performance. The process results in detailed hardware layouts and artwork, net lists, and test vectors that can then be seamlessly transitioned to manufacturing and test via format conversion of the data.

Since most of the software developments are verified during the architecture design phase, they are limited at this point to generation of those elements that are target-specific. This includes configuration files, bootstrap and download code, target-specific test codes, etc. All the software is compiled and verified (to the extent possible) on the final virtual prototype prior to the detailed design review. Design release to manufacturing marks the end of the RASSP design process.

- Prototype Manufacturing, Integration and Test The manufacturing, integration and test processes define for RASSP the interface of design engineering to the disciplines required to build and test signal processor prototypes. This means the interaction of manufacturing and test personnel throughout the design cycle to support concurrent engineering through the release of the virtual prototype to manufacturing. This process also supports subsequent testing of the manufactured design and hardware/software integration of the signal processor.

- Specialty Engineering ('illities, etc.) Specialty engineering covers all the non-design engineering tasks required to successfully develop and field RASSP products. These include reliability, maintainability, parts, and EMI engineering (where applicable), as well as integrated logistic support engineering and services.

**Next:** 2 Introduction **Up:** Appnotes Index **Previous:** Appnote Hardware / Software Codesign Index

Approved for Public Release; Distribution Unlimited Dennis Basara

Next: 3 IDEF3 Representation of Process Workflows Up: Appnotes Index Previous:1 Executive Summary

# RASSP Methodology Application Note

## 2.0 Introduction

### 2.1 Methodology Application Note Objective

The objective of this application note is to provide an understanding of the design methodology developed for the LM/ATL RASSP program. It is not the intent to lead you, the reader, on a step-by-step discussion of this methodology as applied to any one particular application. Rather, it will use the workflows generated in IDEF3X format to lead you through a generic discussion of the RASSP methodology. One must always keep in mind that RASSP is an iterative and concurrent development process. Feedback or 'Failback' paths are identified within the workflows. However, because every program/project is unique, the failback paths may be different for each effort and the number of iterations of each design cycle will also vary.

## 2.2 Organization of the Application Note

Sections 5, 6, 7, and 8 are organized around the IDEF workflows developed for the Systems, Architecture, and Detailed Design processes. Clicking within the major boxes will enable you to explore the hierarchical nature of each of the major process levels. Defining the initial Systems, Architecture, and Detailed Design diagram as the First level, each of the major sections can be navigated to the following levels.

- System Design 3 levels

- Architecture Design 3 levels

- Detailed Design 4 levels

The rest of this application note contains the detailed descriptions of the methodology, the conclusions, and the references for additional detail. Section 3.0 is a high level overview of IDEF (ICAM (Integrated Computer-Aided Manufacturing) Definition). This reference is useful in order to better understand the constructs of IDEF and thus be able to review the process drawings. This allows the reader to get a quick understanding without having to read the detailed explanations.

Section 4.0 contains a description of some of the overall processes that are found throughout the RASSP methodology. They unify the design tasks that are described in subsequent sections. This section starts with a description of the RASSP methodology as a rixk driven iterative hierarchical virtual protoytping, spiral development process. The unifying process of Model Year Architecture, Hardware/Software Codesign, Design-for-Testability, and Reuse Library Management are then presented as a high-level introduction.

Section 5.0 then presents a top level summary of the system, architecture, and detailed design processes. This section provides the first links into the IDEF process flows that can lead the reader graphically through the methodology. These process flow are displayed in a hierarchical fashion and also contain links to the textual descriptions of the process found in Sections 6.0, 7.0, 8.0, and 9.0.

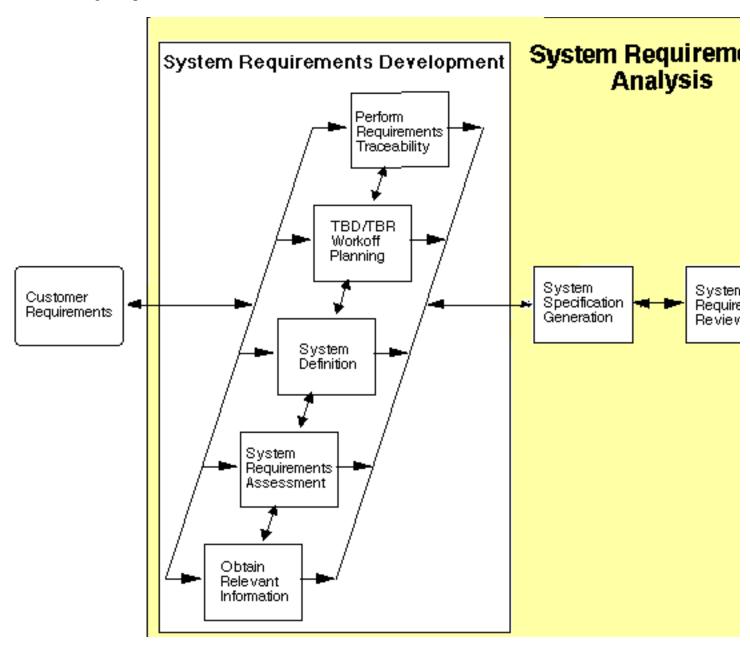

Section 6.0 provides the detailed discussion of the System Design process. It takes you through requirements analysis, functional analysis, system partitioning, and completes by discussing other items that need to be considered during design, i.e., DFT, IPT, design reviews, and use of VHDL in modeling.

Section 7.0 provides the detailed discussion of the Architecture Design process. It takes you through functional design, architecture selection, architecture verification, and software in the architecture design process. It completes with a discussion of other items that need to be considered during design, i.e., DFT,

IPT, design reviews, and use of VHDL in modeling.

Section 8.0 provides the detailed discussion of the Detailed Design process. It takes you through module/MCM design, ASIC design, FPGA design, backplane and chassis design, and subsystem integration and test. It completes with a discussion of other items that need to be considered during design, i.e., DFT and use of VHDL in modeling.

Section 9.0 provides an integrated view of the software development process within the RASSP methodology. This has all been discussed previously in the System, Architecture, and Detailed Design sections since the methodology if a Hardware/Software Codesign one. It is provided here in one place so that those interested in only the software development may have an easier reference.

Section 10.0 provides a discussion of the implementation of a reuse management system that will assist in the design ÔforÕ and ÔwithÕ reuse. This is a key ingredient in reducing cost and cycle time for your designs.

Section 11.0 provides the reference information and the links to those references. It also provides links to all of the other application notes and case studies.

### 2.3 Linkage with other Application Notes

This methodology application note serves as a gateway to all of the other Application Notes and Case Studies created by Lockheed Martin ATL. The case studies (SAR, ETC4ALFS on COTS Processors, and SAIP) will lead you through how this methodology was actually applied and used in the performance of these Benchmark programs. The focus for these case studies is more on what was done and the benefit gained. Not all of the RASSP methodology and process steps were applied to each of the case studies. The Methodology was tailored to meet the goals and objectives of each development project.

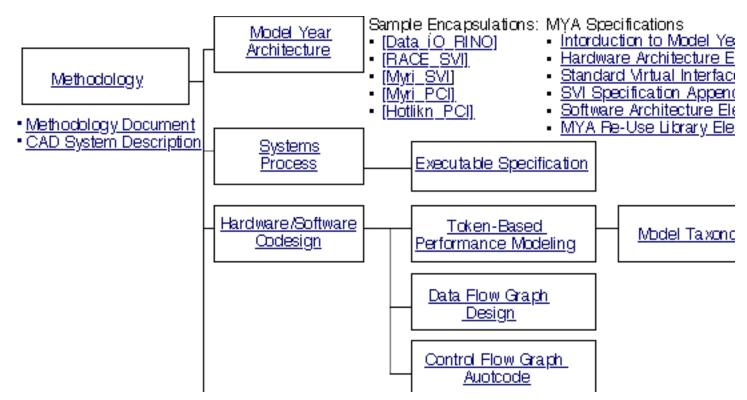

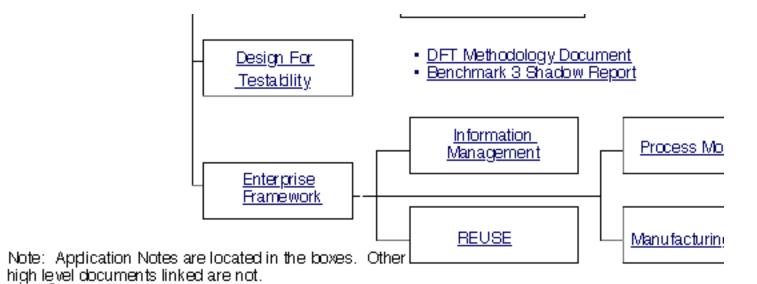

The Application Notes serve to provide specific details of the technologies that were developed and applied within RASSP. Detailed examples were taken from the benchmark programs in order to illustrate not only the how and why it was accomplished but also show the benefits to be gained by applying the RASSP technologies. Figure 2-1 illustrates how each of the application notes are tied to this document. This figure, as well as other links in this document will allow access to the rest of the application notes.

Figure 2 - 1: RASSP Design process.

Each major cycle of the spiral process represents an iteration of a virtual prototype. Within each prototype iteration, pieces of the design can and most likely will be at different levels of maturity, as shown in Figure 4 - 1. Each piece of the design may be represented by a mini-spiral where the spiral cycles correspond to virtual prototypes of the piece. Consequently, for each major spiral cycle, there may be activity in the system, architecture, and detailed design processes.

The overall RASSP development process, shown in Figure 1 - 1, has four major elements:

- Project planning/Management Project planning/management provides the first step of the process: Develop the technical plan, and form the PDT (product development team) and the overall management approach for the specific signal processor development.

- Design Process The design process represents development of the signal processor design from requirements capture through release to manufacturing. Is has three major processes: Systems design, architecture design, and detailed design. This process takes customer requirements and results in a fully verified (functionality and performance) virtual prototype of the signal processor.

- o Systems Design Process This process captures customer requirements and converts these system-level needs into processing requirements (functional and performance). Functional and performance analyses are performed to properly decompose the system-level description. The system process has only a very preliminary notion of either hardware versus software functionality or processor implementation.

- O Architecture Design Process The architecture process transforms processing requirements into a candidate architecture of hardware and software elements. Architecture selection initiates the trade-offs between the different processor architecture alternatives. During this process, the system-level processing requirements are allocated to hardware and/or software functions. The hardware and software functions are verified with each other via 'co-verification" at all steps. The architecture verification process results in a detailed behavioral description of the processor hardware and the definition of the software required for each processor in the system. The intent is to verify all the code during this portion of the design, ensuring hardware/software interoperability early in the design process.

- o Detailed Design As with the prior processes, the design is completed and verified for both hardware and software via a set of detailed functional and performance simulations. When this process is complete, the design is established, resulting in a fully verified virtual

prototype of the system.

During the hardware portion of the detailed design process, behavioral specifications of the processor are transformed into detailed designs (RTL, and/or logic-level) through a combination of hardware partitioning, parts selection, and synthesis. Detailed designs are functionally verified using integrated simulators, and performance/timing is also verified to ensure proper performance. The process results in detailed hardware layouts and artwork, net lists, and test vectors that can then be seamlessly transitioned to manufacturing and test via format conversion of the data.

Since most of the software developments are verified during the architecture design phase, they are limited at this point to generation of those elements that are target-specific. This includes configuration files, bootstrap and download code, target-specific test codes, etc. All the software is compiled and verified (to the extent possible) on the final virtual prototype prior to the detailed design review. Design release to manufacturing marks the end of the RASSP design process.

- Prototype Manufacturing, Integration and Test The manufacturing, integration and test processes define for RASSP the interface of design engineering to the disciplines required to build and test signal processor prototypes. This means the interaction of manufacturing and test personnel throughout the design cycle to support concurrent engineering through the release of the virtual prototype to manufacturing. This process also supports subsequent testing of the manufactured design and hardware/software integration of the signal processor.

- Specialty Engineering ('illities, etc.) Specialty engineering covers all the non-design engineering tasks required to successfully develop and field RASSP products. These include reliability, maintainability, parts, and EMI engineering (where applicable), as well as integrated logistic support engineering and services.

Next: 3 IDEF3 Representation of Process Workflows Up: Appnotes Index Previous:1 Executive Summary

Approved for Public Release; Distribution Unlimited Dennis Basara

Next: 4 Unifying Processes and Roles in RASSP Up: Appnotes Index Previous: 2 Introduction

# RASSP Methodology Application Note

## 3.0 IDEF3 Representation of Process Workflows

#### 3.1 What are Workflows

A workflow consists of a group of process steps to be performed in a particular order to complete a particular design effort. A program plan is created by piecing together the workflow segments which are appropriate to the design task. When instantiated in the enterprise, the workflows can be executed by clicking on the process steps in the order allowed by the precedence relationships and performing the task required by that process step. The concept of operation for the enterprise framework includes the ability for teams of engineers to execute program plans, expressed as workflows. The information manager generates the appropriate objects and work locations to facilitate the workflow. The information models and information manager are therefore closely coupled to the process models and the workflow manager.

The workflows are hierarchical in nature - representing the various disciplines associated with electronic design. The options available to a user organization are either to make use of the workflows in their current form or to develop plans based on a combination of reuse of workflow segments, individual process steps or augmentation of workflow segments with custom user process steps.

### 3.2 Activity Definitions

The Activity Definitions present short descriptions of what is to be accomplished for each process step, as well as the tools and business item names (placeholders) for the inputs, outputs, required personnel resources and reference data needed to perform each task or process step. In execution of the program plan constructed from the workflows, the activities and business item specifications are instantiated for the particular project. As part of this process, users are assigned to the roles in the project.

## 3.3 Workflow Capture

Workflows were developed for the entire RASSP design process using the IDEF3X modeling method. IDEF3X was developed by Rockwell International Corporation and is an extension of the IDEF3 process description capture method. The name IDEF originates from the Air Force program for Integrated Computer-Aided Manufacturing (ICAM) from which the first ICAM Definition, or IDEF, methods emerged. IDEF3 was created specifically to capture descriptions of sequences of activities. It can be distinguished from other process modeling methods because it facilitates the capture of the description of what a system actually does.

#### 3.3.1 IDEF3X Overview

IDEF3X is a modeling method which combines the ICOM (input, control, output, mechanism) aspect of IDEF0 with the process flow description of IDEF3, along with some additional features to facilitate implementation by a workflow management tool such as Intergraph's Design Methodology Manager (DMM). The syntactic elements of an IDEF3X model are similar to IDEF3 and include units of behavior (UOBs), junction boxes, and precedence links. Additional features include identifying ICOMs by naming the object and its life cycle state separated by an "\*" (e.g., Draft\*Publication - where Publication is the name of the object and Draft is its current state), object state links which identify the flow of data between UOBs, feedback links which indicate failback paths, annotating the name of the junction boxes with an "A" or "S" to indicate an asynchronous or synchronous junction (e.g. A&), and annotating the precedence links with a "P:" followed

by a two-letter code which indicates the precedence between the parent and dependent UOB.

Synchronization refers to the relative timing of the process paths that either converge into or diverge out of a junction. A synchronous fan-in junction indicates that all processes connected to the input of the junction must complete simultaneously before the UOB connected to the output of the junction will be activated. If the fan-in is asynchronous, there is no timing constraint imposed on the completion of the input processes.

#### 3.3.2 Precedence Links

A precedence link is defined by two states such as Finish-Start which is the default precedence of links within an IDEF3 process model. The first state indicates the state the parent UOB (where the link starts) must be in before the dependent UOB (where the link ends) can enter the second state. So, Finish-Start means the parent UOB must finish before the dependent UOB can start. IDEF3X identifies additional precedence relationships which are supported by Intergraph's DMM tool. These 8 precedence are:

- Start Start: The dependent process can begin a soon as the parent process begins, but not before. No completion order is implied.

- Start Finish: The dependent process cannot complete successfully until the parent process starts. No starting order is implied.

- Finish Start: The dependent process cannot begin until the parent process completes with the chosen exit status (exit statuses are defined by the implementation)

- Finish Finish: The dependent process cannot complete successfully until the parent process completes with the chosen exit status. Either process may begin first.

- Concurrent: This is a combination of Start-Start and Finish-Finish. The dependent process cannot begin until the parent process begins, and cannot be completed until the parent process completes with the chosen exit status.

- Cascade: The dependent process cannot begin until the parent process completes with the chosen exit status, and is immediately and automatically invoked when the parent process completes with that status. Cascade connections are used to automatically trigger processes when the design passes a certain point.

- Fail (Reset): The dependent process and any downstream processes are marked as invalidated when the parent process completes with a status that activates a fail connection. It is useful to think of the fail connection as "Reset" -- it resets the workflow to a previous state based on a particular exit status that may or may not be a true "failure" condition.

- Fail Cascade: When a process completes with a status that activates a fail-cascade connection, the dependent process and all downstream processes are marked as never having started. The dependent process connected to the fail-cascade link is immediately launched.

This information will be represented on the workflows by placing a 'P' on the link followed by a ":" and the 2 letter code. For example,

P:SS for Start - Start P:SF for Start - Finish P:FS for Finish - Start P:FF for Finish - Finish P:CO for Concurrent P:CA for Cascade P:FR for Fail (Reset) P:FC for Fail - Cascade

### 3.4 Modeling Example

The workflow model captures:

- Process steps

- Precedence relationships between process steps

- Personnel roles authorized/required to perform workflow

- Information objects involved (created, used, modified, destroyed, etc.) in the process step

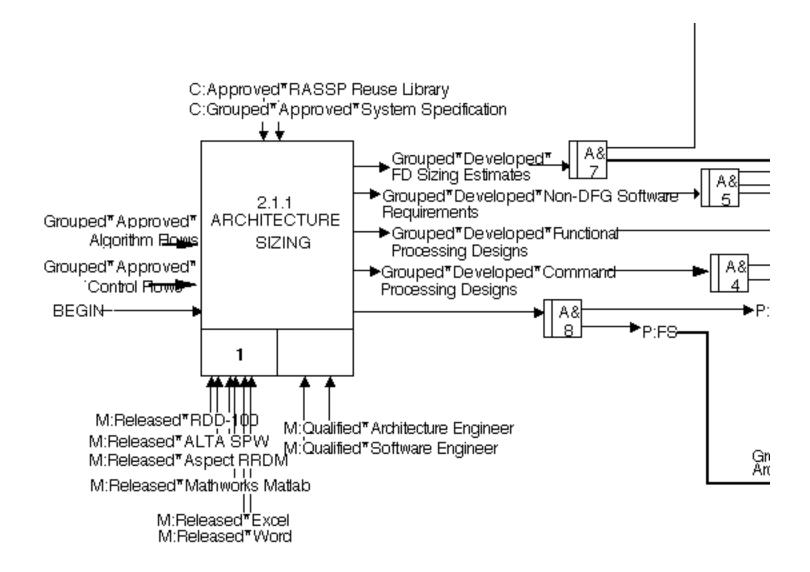

- Tools to be launched or controlled at each step

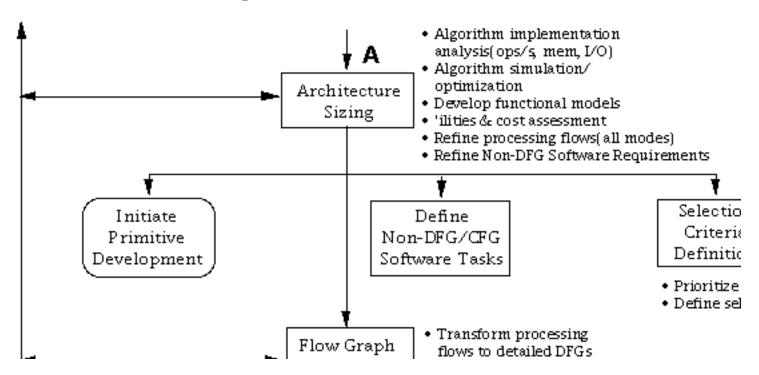

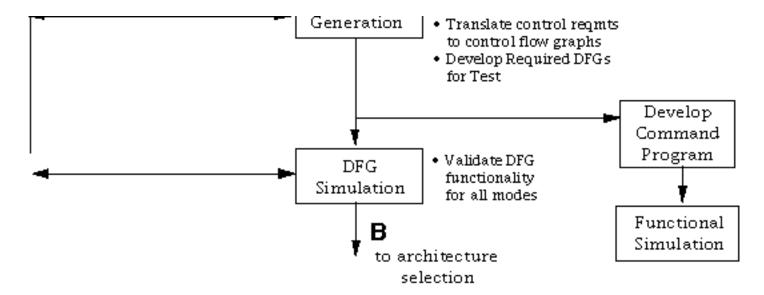

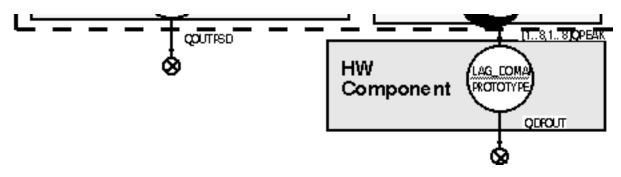

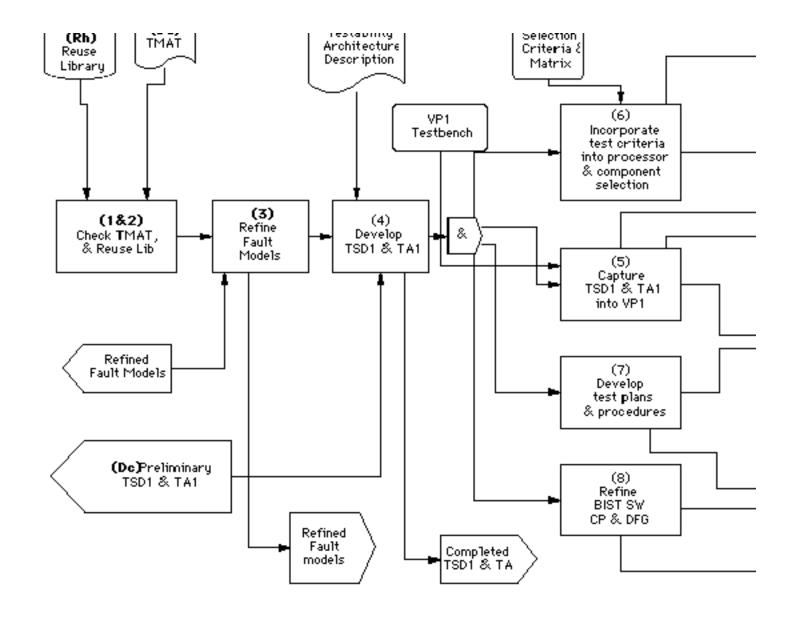

The example elaborated in this section is taken from the RASSP Architecture Definition: Functional Design workflow. Figure 3 - 1 contains a portion of the Functional Design workflow represented as an IDEF3X model. The model contains three units of behavior (UOBs) which represent design activities: Architecture Sizing, Selection Criteria Definition and Refine DFT Strategy. Also present in this model are precedence links, object state links, junction boxes, and all of the Inputs, Controls, Outputs and Mechanisms (ICOMs) for each UOB. This model was developed using the TopDown Flowcharter tool by Kaetron Software Corporation.

Although it is not the purpose of this Appendix to present IDEF3X concepts in depth, a quick review is in order. The text attached to the UOBs are called Business Items. These are place holders for actual file system items which contain the design data. There are four different types of Business Items or ICOMs. The inputs and outputs are self-explanatory. The controls are documents that can be referred such as libraries or specifications. The Mechanisms are the tools and personnel resources required to execute the process step. The syntax of an input or output Business Item is:

[Grouped]\*State\*Business\_Item\_Name.

The [Grouped] term is optional. If it is present, (as in Grouped\*Developed\*SD Test Architecture and TSD 2.1.3 in Figure 3 - 1), it indicates that the Business Item actually consists of multiple file system items (files or directories). For example, Grouped\*Developed\*SD Test Architecture and TSD is made up of the file system entities:

Developed\*SD Test Architecture Developed\*SD TSD Developed\*SD Test Plans Developed\*SD Test Procedures Developed\*SD Fault Model

The word "Developed" indicates the state of the Test Architecture and TSD. In this case, the data items have just been created during the process step 2.1.3.

Figure 3 - 1: IDEF3X Workflow Model.

Other states which are used are:

Developed: An item which has just been created during a process step Updated/Refined: A "Developed" item which has been updated/refined during a process step

Preliminary/Verified: An "Updated" item which has been refined and (possibly) simulated and is ready to be approved

Approved: A "Preliminary/Verified" item which has gone through some type of approval or Design Review cycle. The actual level of approval necessary to transition an item to an "Approved" state varies depending on the particular instantiation of the Design Reviews. It can vary from workflow to workflow and also from one implementation to another. There are several different states available:

Generated: An item which is automatically produced from a tool

Qualified: Refers to the skill designation which a person must have in order to be able to execute the process step

Responsible: Indicates which personnel resource will have the authority to transition the process step

Released: Refers to the status of a tool (Currently this is the only status used for tools)

Variable: Indicates that the data item is a pointer to a group of data items, one of which will be chosen based on decisions made during the execution of the program plan. For example, a particular processor may be chosen during a process step. Further on in the program plan, the generic code for that processor will be targeted using a library specific to that processor. The target library for the processor is one of the members of the "Variable\*Target Libraries" (on the Architecture Definition:Architecture Verification Workflow).

In Figure 3 - 1, the workflow begins with the process step Architecture Sizing. In the Activity Definitions, it indicates that the purpose of this activity is to analyze the system requirements and processing flows for all required modes in terms of estimated operations per second, memory requirements, and I/O bandwidths. The resulting functional processing flows represent the detailed algorithms that must be performed for each required mode.

The inputs for this activity are the Business Items: Grouped\*Approved\*Algorithm Flows Grouped\*Approved\*Control Flows

The controls for this activity are:

Approved\*RASSP Reuse Library

Grouped\*Approved\*System Specification

The outputs for this activity are:

Grouped\*Developed\*FD Sizing Estimates

Grouped\*Developed\*Non-DFG Software Requirements

Grouped\*Developed\*Functional Processing Designs

Grouped\*Developed\*Command Processing Designs

The tool mechanisms are: Released\*RDD? Released\*Aspect RRDM Released\*ALTA SPW Released\*Mathworks MATLAB Released\*EXCEL Released\*WORD

The personnel mechanisms are: Qualified\*Architecture Engineer Qualified\*Software Engineer

The other two activities can be analyzed similarly. It is important to distinguish between junction boxes which are used to distribute/collect data to/from multiple process blocks and junction boxes which are used to indicate precedence. Some Business Items which are outputs of 2.1.1 are directed to 2.1.2 and 2.1.3 via asynchronous "AND" junction boxes. In this case, no timing is implied. Note that similar boxes are used to direct the precedence links out of 2.1.1 to 2.1.2 and 2.1.3. These precedence links indicate that when 2.1.1 finishes, 2.1.2 and 2.1.3 become startable.

For readability purposes, the attached leaf-level Architecture workflows do not have the precedence links indicated on them.

## 3.5 Summary

This section will serve as a reference for developing program plans. It describes what workflows and Activity Definitions are and how they pertain to the RASSP Methodology in general and the Enterprise, in particular. The workflows should be viewed as templates which can be pieced together to create a program plan. The

Activity Definitions contain supplemental information about each process step.

Next: 4 Unifying Processes and Roles in RASSP Up: Appnotes Index Previous:2 Introduction

Approved for Public Release; Distribution Unlimited Dennis Basara

Next: 5 Process Up: Appnotes Index Previous:3 IDEF Representation of Workflows Process

# RASSP Methodology Application Note

## 4.0 Unifying Processes and Roles in RASSP

# **4.1 Risk Driven Iterative Hierarchical Virtual Prototype Process (spiral model)**

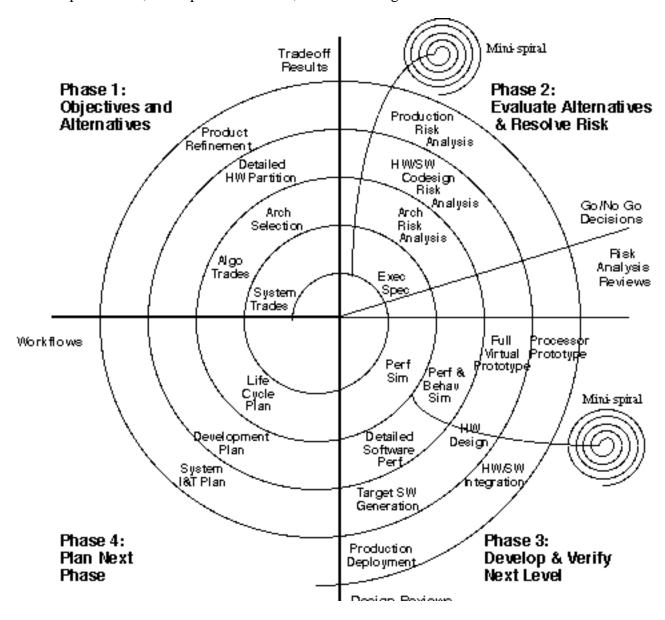

The goals of the RASSP program, which include rapid prototyping combined with continual process and product improvements, are more applicable to an iterative, spiral development model than the traditional waterfall development model. The spiral model was originally directed at supporting the software development process. Since the RASSP scope includes more than just software, adaptation of the model is appropriate. A view of the spiral model, as adapted for RASSP, is shown in Figure 4 - 1.

Figure 4 - 1: RASSP spiral model

Four phases are associated with each major cycle of the spiral. In the first phase, the baseline approach and appropriate alternatives are developed to meet program objectives. During the second phase, the approaches are evaluated against the objectives and alternatives, and the risk associated with these approaches is evaluated. During the third phase, the prototype is evaluated and the next level of the product is developed. This phase results in a prototype of the design. In the fourth phase, the product is reviewed and plans for the next development stage are established. This entire process is repeated to the next level of detail by repeating each of the four phases; hierarchical application of the process results in an interactive, risk-driven approach to rapid prototyping.

In the traditional spiral model for software, each cycle might be a full set of software at some level of functionality and/or maturity, or might have critical portions of functionality prototyped (with others "stubbed" out for implementation in subsequent cycles). RASSP applies the concept of virtual prototypes, or simulated versions of the signal processor (encompassing hardware/software functionality and performance) at each cycle of the spiral. During each spiral iteration, a new virtual prototype emerges-from executable specification to high-level behavioral prototype, and then to full functional and timing versions of the design. The design then transitions into a full hardware prototype and matures into a design for full-scale production. Risk analysis and design reviews provide decision points within the cycle and enable backtracking to evaluate alternatives. New spirals are spawned to reduce high-risk elements or continue the design as planned. This model represents a more temporal overlay to the RASSP functional processes and supports concurrency (overlap) between functional disciplines.

In the RASSP methodology the spiral process is applied hierarchically. Each data package may be the result of a series of mini-spirals, while also being part of the primary set of spirals within the design. As high-risk elements in the design process are indentified, "mini-spirals" can be spawned to develop critical items that are "long poles" in the design schedule. Note that this approach allows development across processes as a function of time [e.g., architecture or detailed design tasks can be performed during the early stages (systems process) for high-risk portions of the design]. The logical consequence of the process is that each successive virtual prototype has more complete functionality than its predecessor.

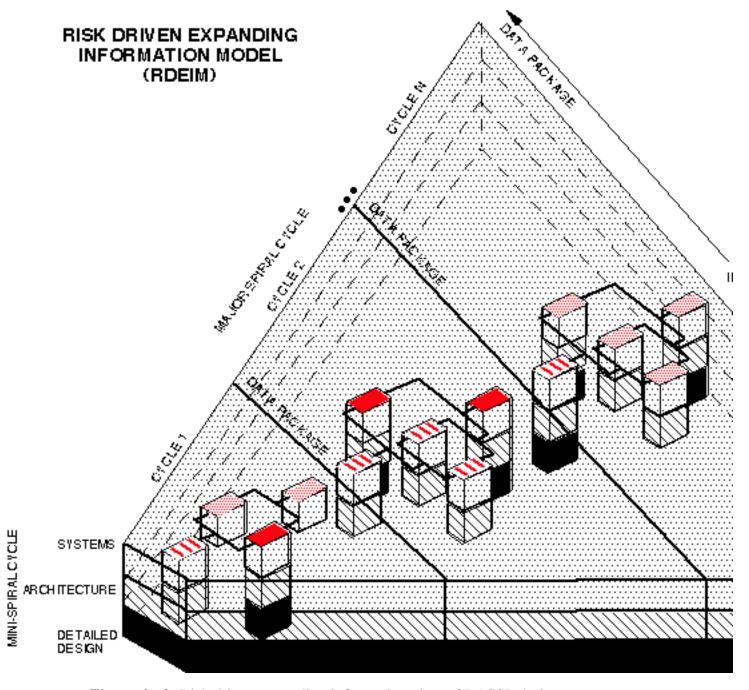

An expanding information view of the spiral process is shown in Figure 4 - 2. The major spiral cycles correspond to the iterations of a virtual prototype associated with the overall signal processor. The mini-spiral cycles correspond to the system, architecture, and detailed design processes associated with portions of the design and/or models (e.g. custom processor, MCM, new hardware model, new software primitive, etc.). This view corresponds to the idea that, based upon risk, pieces of the overall design may be at differing levels of maturity. At the same time, there must be a minimum maturity level achieved and data package produced for the overall signal processor to proceed from one major spiral cycle to the next. The data packages form the basis for the design reviews associated with each major spiral; these are used to drive the next iteration of the design. The data packages are inputs to (and become a subset of) the next stage of the process.

The concept of the virtual prototype as an expanding information model of the processor maps well into this paradigm. At all steps of the design, the model is characterized by four major elements-workflows, requirements, executable models, and test benches. The four elements are summarized as follows:

- 1. Workflows The steps used to develop the current/next phase of the development. This is the result of the fourth phase of the spiral model.

- 2. Requirements An appropriate set of parameters specifying the performance and implementation goals for the processor (size, weight, power, cost, schedule, etc.).

- 3. Executable Models The functional and structural definition of the processor under development. VHDL is being heavily emphasized to specify functionality throughout the design process on RASSP.

4. Test Benches - An appropriate set of test vectors, data sets, etc. that fully verify the functionality and performance of the model. We intend to use VHDL (and the corresponding WAVES standard) to the greatest extent possible for RASSP test benches.

Figure 4 - 2: Risk driven expanding information view of RASSP design process

## 4.2 Role of Model Year Architecture in the RASSP Methodology

To enable design reuse and minimize upgrade costs, a set of common hardware and software architecture elements is required. A key element to implement this methodology is the selection of a Model Year Architectural approach (both hardware and software) that adheres to the following principles:

• The architectures must be open, promoting hardware/software upgradability and reusability in other

- applications

- The architectures must use emerging, state-of-the-art commercial technology whenever possible

- The architectures must support a range of applications to maintain low non-recurring engineering costs

- The architectures must facilitate continuous product improvement

The following section summarizes the approach taken for defining the concept of a Model Year Architecture. A more complete description of the technology, additional references, and actual encapsulations can be found in the Model Year Architecture (MYA) application note.

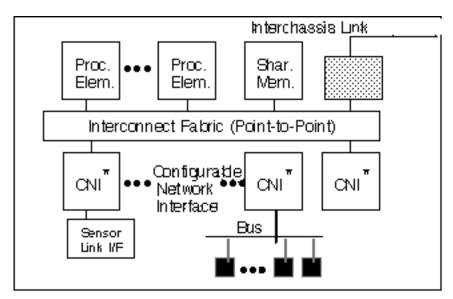

The Lockheed Martin ATL approach to implementing the Model Year Architecture is based on modular, scalable architectures that use functional standard interfaces. This approach strives to move beyond today's approach of standardizing on physical interfaces; this approach is good, but it does not go far enough to ensure technology independence. Physical interfaces encompass the lower levels of the ISO/OSI protocol hierarchy and are specific to the media and operating conditions (voltage, timing, etc.) specified by these layers. Functional interfaces provide the data-transaction-level capabilities to support communications, independent of the underlying physical technology. By standardizing on functional interfaces, we can maximize independence from technology (electrical versus optical) and specific hardware versus software (processor-based versus dedicated hardware) approaches. We will apply this approach to a number of signal processing interfaces required for RASSP, as shown in Figure 4 - 3. The RASSP team has developed a full description of this approach, which is documented in a set of specifications that can be found in the MYA application note.

Figure 4 - 3: RASSP Model Year Architecture

The RASSP Model Year Architecture(s) must be supported by the necessary library models to facilitate trade-offs and optimizations for specific applications. Reusable hardware and software libraries facilitate growth and enhancement in direct support of the RASSP Model Year concept. The hardware and software components within the library are encapsulated by the functional wrappers required to enable efficient integration and use. We used the Model Year Architecture methodology to develop all elements for inclusion and use within the reuse libraries. This is key to attaining the 4X cycle-time improvements on RASSP. As technology advances, new architectural elements may be included in the library. Rapid insertion of a new element into an existing RASSP-generated design is the goal of the Model Year concept.

## 4.3 Role of Hardware/Software Codesign in the Methodology

Hardware/software codesign is the joint development and verification of hardware and software through the use of simulation and/or emulation; it begins with initial partitioning and proceeds through to design release.

This section provides an overview of the hardware/software codesign definitions and technologies developed for RASSP. A more complete discussion along with specific application examples can be found in the Hardware/Software Codesign application note.

The principal benefits of hardware/software codesign are:

- Mutual Influence of Both Hardware and Software Early in the Design Cycle Software performance becomes one of the criteria for selecting an architecture, rather than the more traditional approach of selecting the architecture and forcing the software to fit.

- Continual Verification Throughout the Design Cycle As the design progresses through subsequent levels of detail, both hardware and software are continually verified to improve design quality. This minimizes iterations after the design is released to manufacturing.

- Enables Evaluation of Larger Design Trade Space Interoperability of tools and automation of codesign early in the architecture process significantly improves the ability to consider designs which otherwise may be ignored.

- Reduces Integration and Test Since hardware and software have been co-verified throughout the design process, integration and test is greatly simplified. Test and diagnostics are developed up-front, while there is still the opportunity to impact the design for testability.

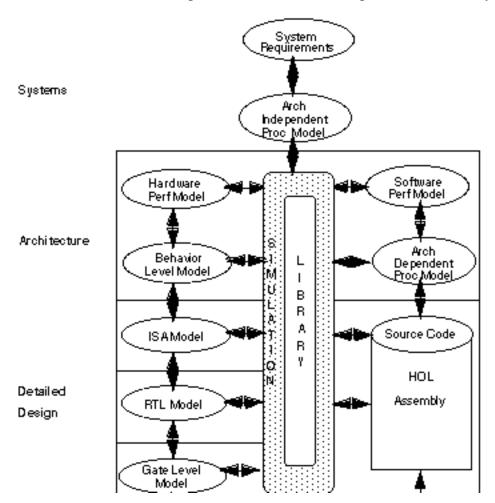

The RASSP design process is based on true hardware/software codesign and is no longer partitioned by discipline (e.g. hardware and software), but rather by the levels of abstraction represented in the system, architecture, and detailed design processes. Figure 4 - 4 shows the RASSP methodology as a library-based process that transitions from architecture independence to architecture dependence after the systems process.

Figure 4 - 4: Hardware/software codesign in RASSP design process

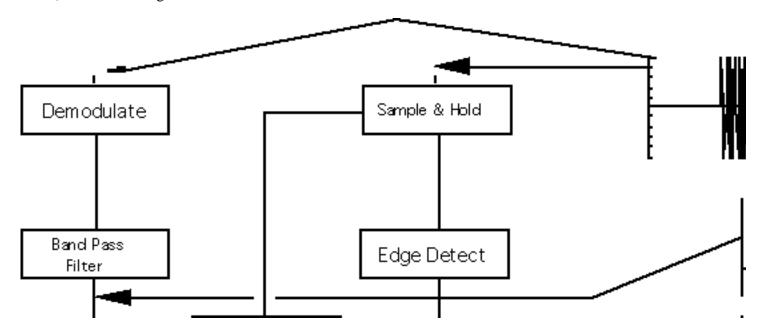

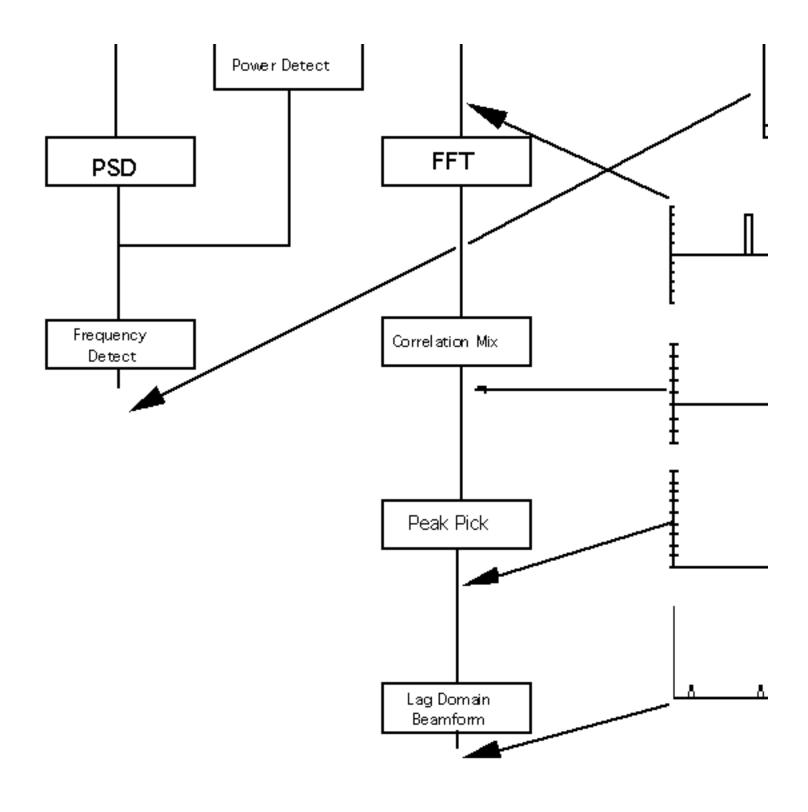

In the systems process, processing requirements are modeled in an architecture-independent manner. Processing flows are developed for each operational mode and performance timelines are allocated based upon system requirements. Since this level of design abstraction is totally architecture-independent, hardware/software codesign is not an issue.

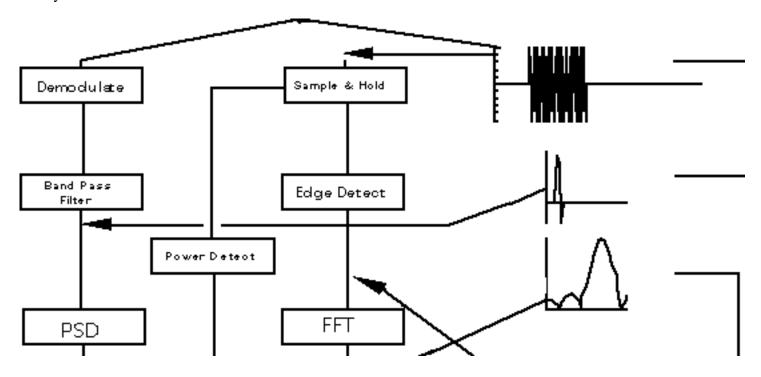

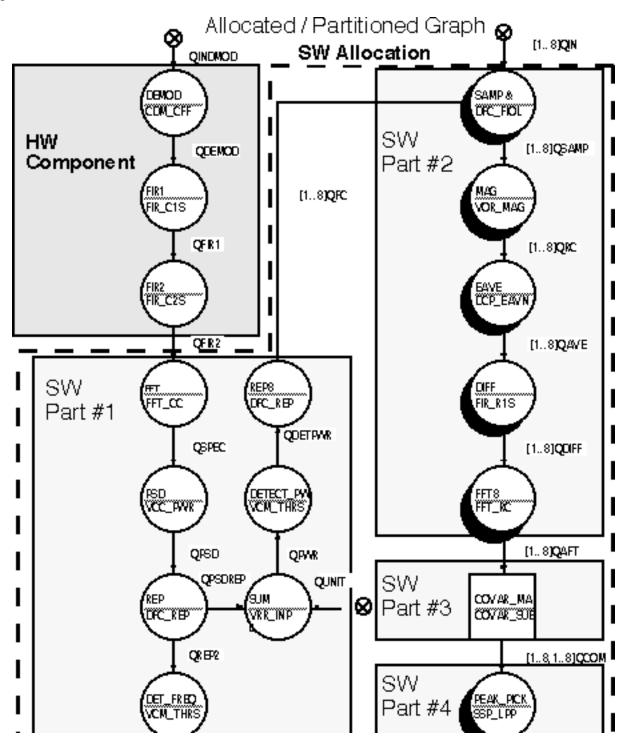

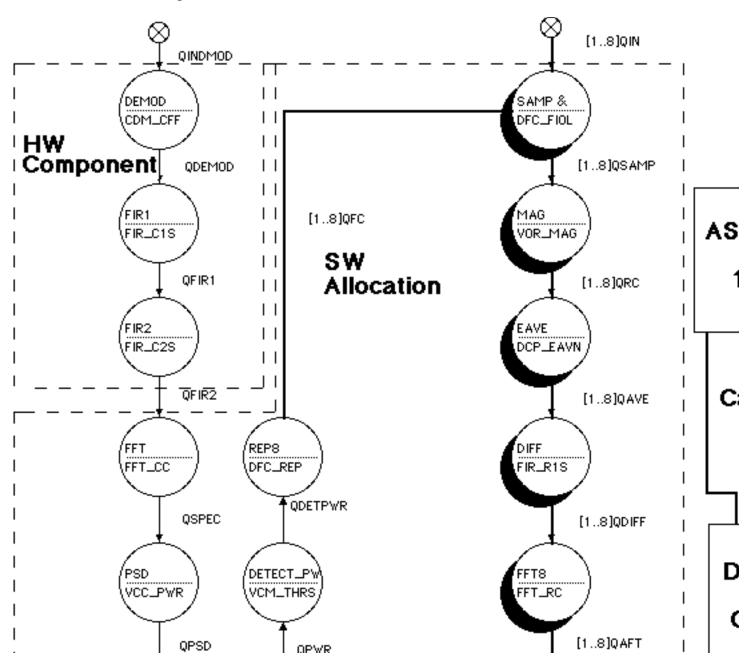

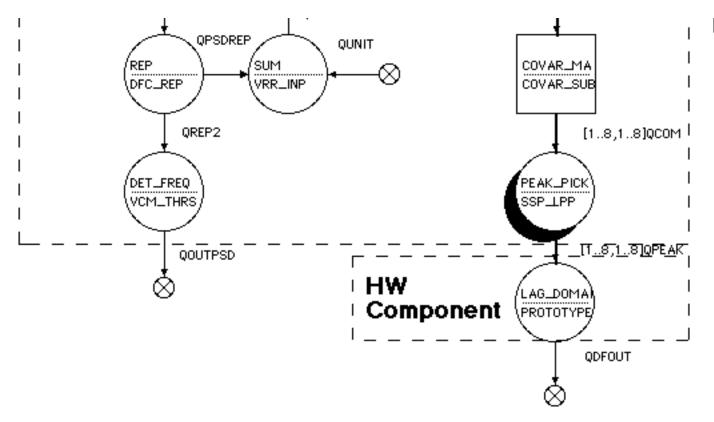

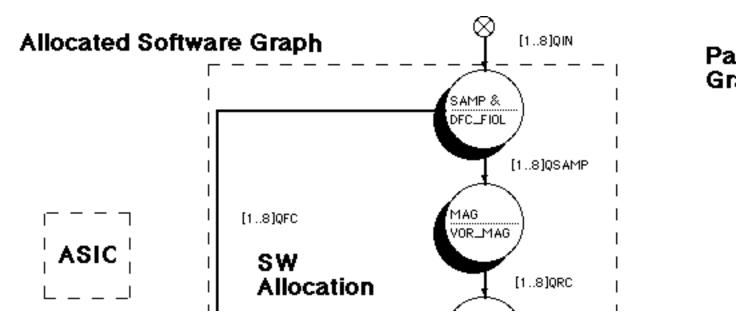

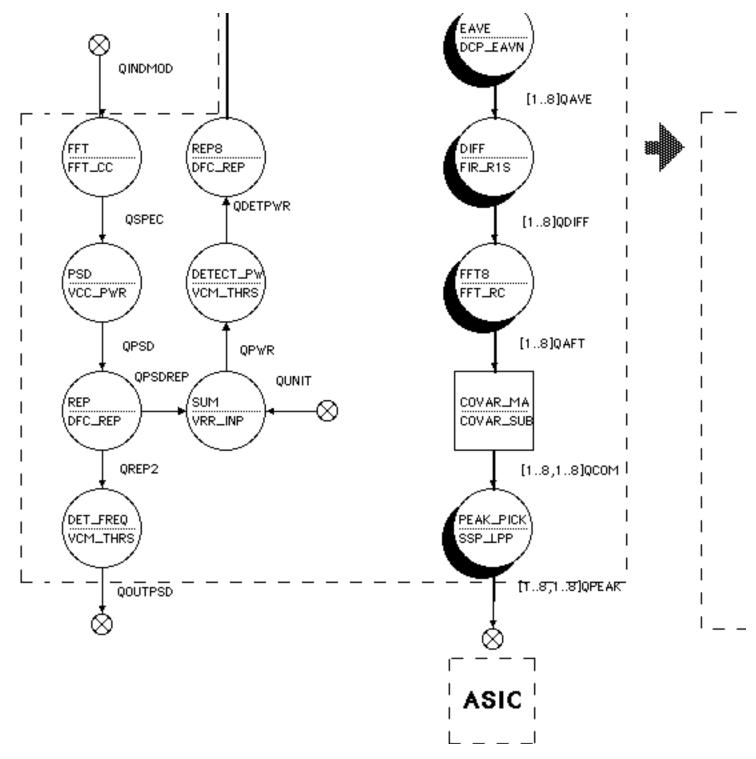

In the architecture process, the processing flows are translated to a standard data and control flow graph description for subsequent processes. The processing described by the nodes in the data flow graph are allocated to either hardware or software as part of the definition of candidate architectures. This becomes the transition to architecture dependence. Requirements and tasks for non-DFG based software and the corresponding software are developed to the maximum extent possible.

The hardware/software allocation is analyzed via modeling of the software performance on a candidate architecture through both software and hardware performance models. For architectures selected for further consideration, hierarchical verification is performed using finer grain modeling at the ISA level and below.

During the detailed design process downloadable, executable application and test code is verified to the maximum extent possible.

Reuse library support is an important part of the overall process. The generation of both hardware and software models is supported in the overall methodology. Software models are validated using the appropriate test data. Hardware models are validated using existing validated software models. Both hardware and software models are iterated jointly throughout the design process.

## 4.4 Role of Performance Modeling/Virtual Prototyping in the Methodology

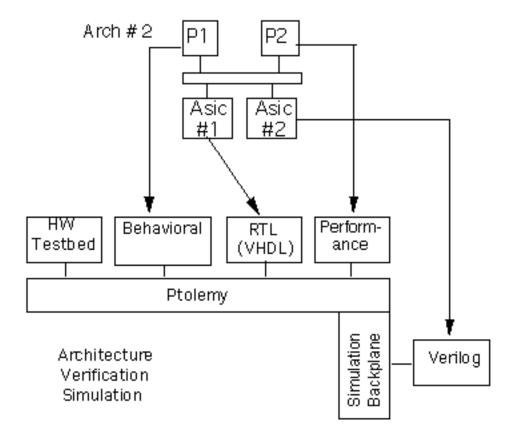

Simulation is an integral part of hardware/software codesign. Figure 4 - 5 shows a top-level view of the overall simulation philosophy in the RASSP methodology. During the systems process, functional simulation is performed to establish a functional baseline for the signal processor.

During the architecture process, various simulations are performed at differing levels of detail as the design progresses. Early in the process, performance simulations are executed using high-level models of both hardware and software from the reuse library. Software is modeled as execution time equations for the various processors in the architecture. Models at the behavioral level, for both processing elements and communication elements, are used to describe the architecture. This level of performance simulation enables rapid analysis of a broad range of architectural candidates composed of various combinations of COTS processors, custom processors, and special-purpose ASICs. In addition, many approaches to partitioning the software for execution of the architecture can be rapidly evaluated. Additional detailed information regarding the role and use of simulation can be found in the following application notes:

- Token-Based Performance Modeling

- Virtual Prototyping

- VHDL Modeling Terminology and Taxonomy

Figure 4 - 5: RASSP simulation philosophy by design process

As the architecture process progresses, each graph partition is translated into a software module for execution on a specific processor in the architecture. Functional simulation is used to verify that the generated code is consistent with the functional baseline. Performance simulation using lower-level models, which include the operating system, scheduling, and support software characteristics, provide the next level of assurance that all throughput requirements are met. Source code for non-DFG based software is developed and tested to the maximum extent possible. Finally, hierarchical architecture verification of the architecture is established using selective performance and functional simulation at the ISA and/or RTL level. The goal is to ensure that all architectural interfaces have been verified.

In the detailed design process, selective performance and full functional simulation are again performed. At this point, however, the design has progressed to where simulation at the RTL and logic-levels is most appropriate. Verification of the designs at this level is necessary before release to manufacturing. It is important to note that pieces of the design may be in different stages of the overall process based upon the risk analysis performed in each development cycle. For example, if it is obvious to the designers during systems analysis that a new custom hardware processor will be required to meet the requirements, the design of the custom processor may be accelerated while the overall signal processor design is still in the architecture process. This approach corresponds to the mini-spirals described in Section 4.1.

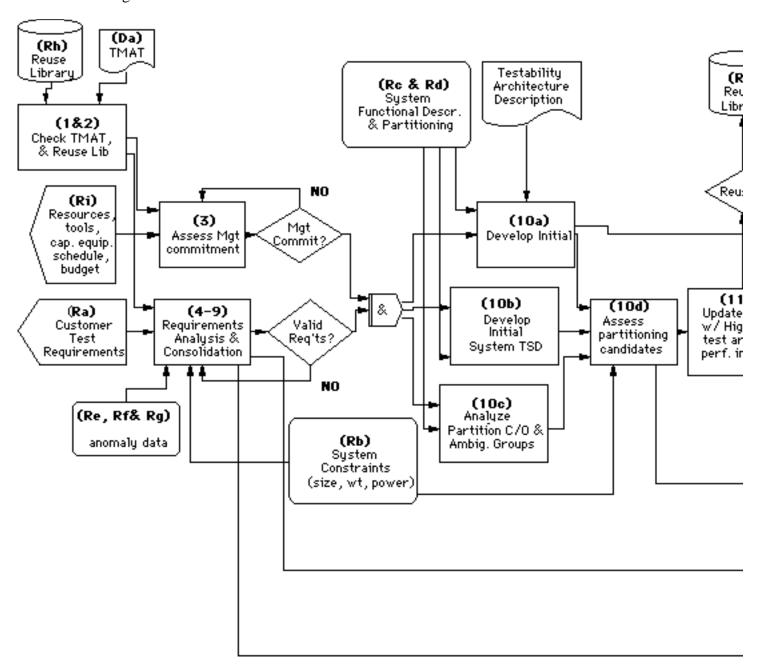

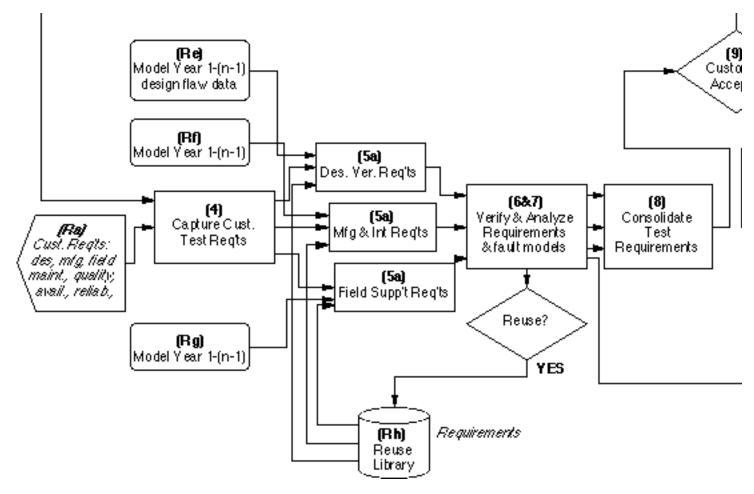

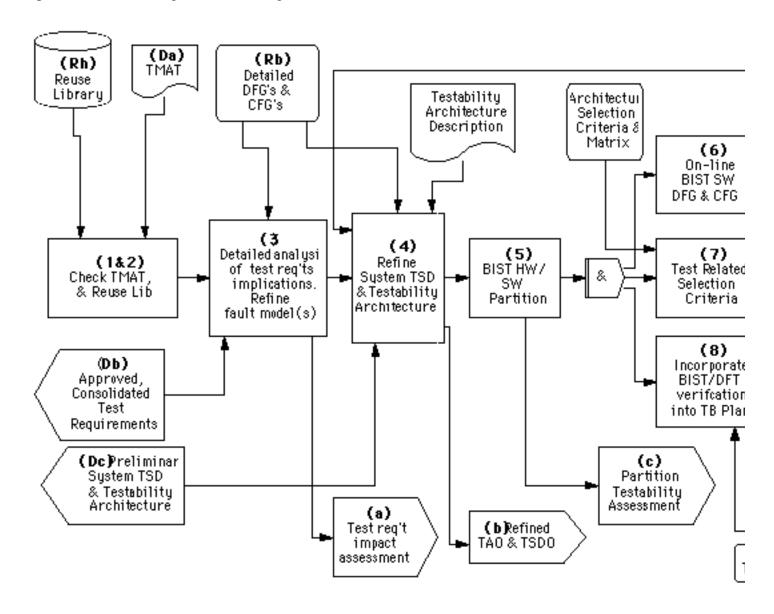

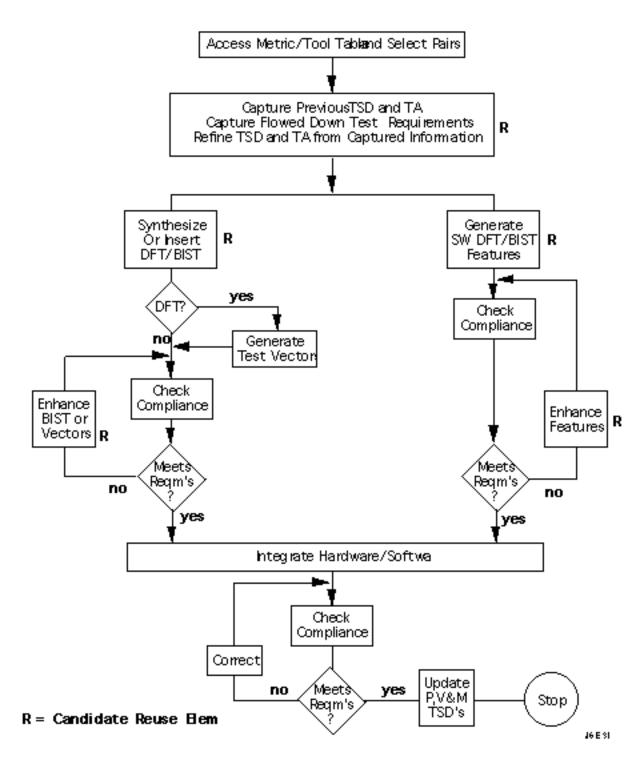

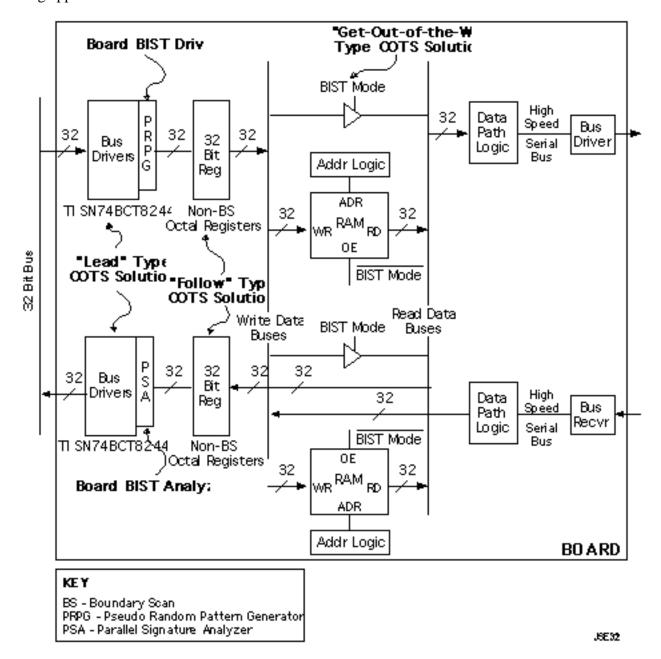

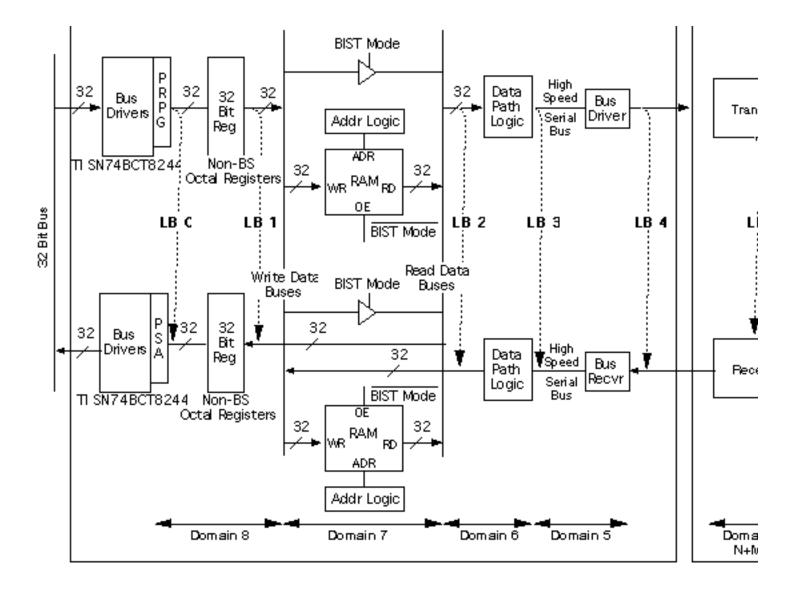

## 4.5 Role of Design For Testability in the Methodology

The Design For Testability (DFT) steps within the overall methodology enables designers to create systems that can be cost-effectively tested throughout their life cycle. Designs that adhere to the methodology are made

testable on the basis of various design for testability (DFT) and built-in-self-test (BIST) techniques. The methodology covers various aspects of test and diagnosis at the chip, MCM, board and system levels, including test requirements capture; test strategy development; DFT and BIST architecture development; DFT and BIST design and insertion; test pattern generation; test pattern evaluation; and test application and control. The methodology provides the designer with a process for introducing testability requirements and constraints early in the design cycle and for addressing DFT and BIST issues hierarchically at the chip, multichip module (MCM), board, and system levels. The payback for early testability emphasis includes lower test cost throughout the life cycle of the product, reduced design cycle time, improved system quality, and enhanced system availability and maintainability.

Elaboration of the DFT steps within the overall methodology can be found in the Design For Testability application note. This application note provides additional detailed references for adopting the DFT methodology. There is a close relationship between the DFT Methodology document and the overall RASSP Methodology Document. DFT and test activities are incorporated into the overall methodology document at a high level. The DFT Methodology document describes these activities in more detail and how they interface with other design activities.

**Next:** 5 Process **Up:** Appnotes Index **Previous:**3 IDEF Representation of Workflows Process

Approved for Public Release; Distribution Unlimited Dennis Basara

**Next:** 6 System Design Process Detailed Description **Up:** Appnotes Index **Previous:**4 Unifying Processes and Roles in RASSP

# RASSP Methodology Application Note

## 5.0 RASSP Design Process Description

#### 5.1 Overview

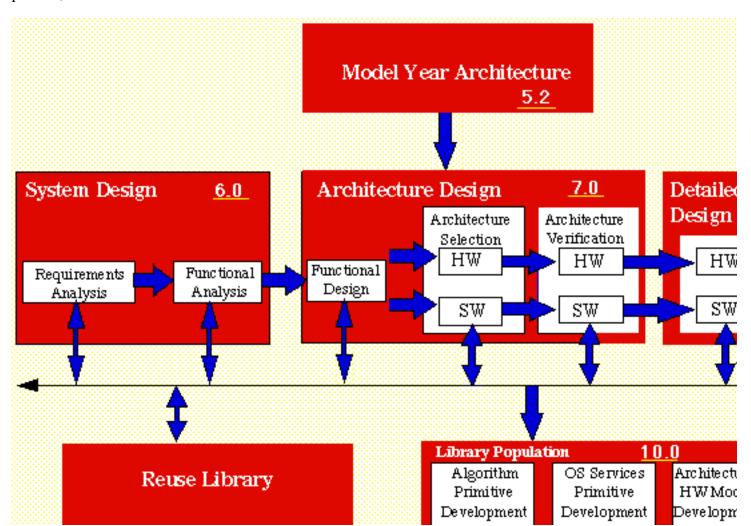

This section addresses the portion of the overall methodology that relates to the RASSP design process. The design process is detailed in Figure 5 - 1. The system design, architecture design, detailed design processes, and library population are addressed in individual subsections. [Click in the shaded boxes of Figure 5 - 1 to obtain the textual overview for that box as well as additional links for more detailed descriptions] Software is discussed in the architecture, detailed design, and library population processes as part of hardware/software codesign; it is also addressed separately to present a consolidated picture. The bold arrow between the individual processes and the library population in Figure 5 - 1 is meant to convey that the overall methodology is an iterative process with feedback from any process to preceding processes. The development of new library elements (software primitives or architectural elements) can be initiated anywhere within the design process, as the need arises.

#### Figure 5 - 1: RASSP design process

Exploring the RASSP design process may be performed in multiple ways in this Section as follows:

- 1. Click in the shaded boxes of Figure 5 1 and a textual overview of the process will be provided. Additional links to more detailed descriptions will also be provided. links will also be found to the Application Notes that provide specific information on various process steps and technology that are employed.

- 2. Click on RASSP Design Process and the top-level IDEF3X process chart will be displayed. From this top level you can link to the lower, leaf level. IDEF charts that detail the system, architecture. and detailed design phases of RASSP. Links are also provided back to the textual descriptions.

Table 5 - 1 list all of the process steps for RASSP and provides direct links not only to the detailed IDEF3X chart but also to the workflow implementation of that process with the Intergraph Design Methodology Manager. As in the second option above, links to the textual description are also provided.

| Design Phase                               | IDEF3X Model | DMM Workflow |

|--------------------------------------------|--------------|--------------|

| System Design                              | X            |              |

| Requirements Analysis                      | X            | X            |

| Functional Analysis                        | X            | X            |

| System Partitioning                        | X            | X            |

| Architecture Design                        | X            |              |

| Functional Design                          | X            | X            |

| Architecture Selection                     | X            | X            |

| Architecture Verification                  | X            | X            |

| Detailed Design                            | X            |              |

| ASIC Preliminary Design                    | X            | X            |

| ASIC Preliminary Design Review             | X            |              |

| ASIC Final Design                          | X            | X            |

| ASIC Pre-Release Design Review             | X            |              |

| ASIC Fabrication and Unit Test             | X            | X            |

| Backplane Preliminary Design               | X            | X            |

| Backplane Preliminary Design Review        | X            |              |

| Backplane Final Design                     | X            | X            |

| Backplane Pre-Release Design Review        | X            |              |

| Backplane Fabrication and Unit Test Design | X            | X            |

| Backplane Final Design Review              | X            |              |

| Chassis Preliminary Design                 | X            | X            |

| Chassis Preliminary Design Review          | X            |              |

| Chassis Final Design                       | X            | X            |

| Chassis Pre-Release Design Review          | X            |              |

|                                            |              |              |

| FPGA Design                      | X | X |  |

|----------------------------------|---|---|--|

| FPGA Preliminary Design Review   | X |   |  |

| Module Preliminary Design        | X | X |  |

| Module Preliminary Design Review | X |   |  |

| Module Final Design              | X | X |  |

| Module Pre-Release Design Review | X |   |  |

| Module Fabrication and Unit Test | X | X |  |

| Module Final Design Review       | X |   |  |

**Table 5 - 1:** RASSP Process Models and Workflows

#### 5.2 Model Year Architecture Overview

To dramatically improve the process by which complex digital systems are specified, designed, documented, manufactured, and supported requires a signal processing design methodology that recognizes a number of application domains. Within these domains are many common characteristics that can be served by the same hardware and software architectures. A key element to implement this methodology is a Model Year Architecture approach (both hardware and software) that adheres to a specific set of principles:

- The architectures must be open to promote hardware/software upgradability and reusability in other applications

- The architectures must use emerging, state-of-the-art commercial technology whenever possible

- The architectures support a wide range of applications to maintain low non-recurring-engineering (NRE) costs

- The architectures must facilitate continuous product improvement and substantial life-cycle-cost (LCC) savings in fielded system upgrades

The RASSP Model Year Architecture(s) must be supported by the necessary library models to facilitate trade-offs and optimizations for specific applications. Reusable hardware and software libraries facilitate growth and enhancement in direct support of the RASSP Model Year concept. The notion of Model Year upgrades is embodied in the reuse libraries and the methodology for their use. As technology advances, new architectural elements may be included in the library. Rapid insertion of a new element into an existing, RASSP-generated design is the goal of the Model Year concept. Details of the Model Year Architecture concept are more fully discussed in the Model Year Architecture application note.

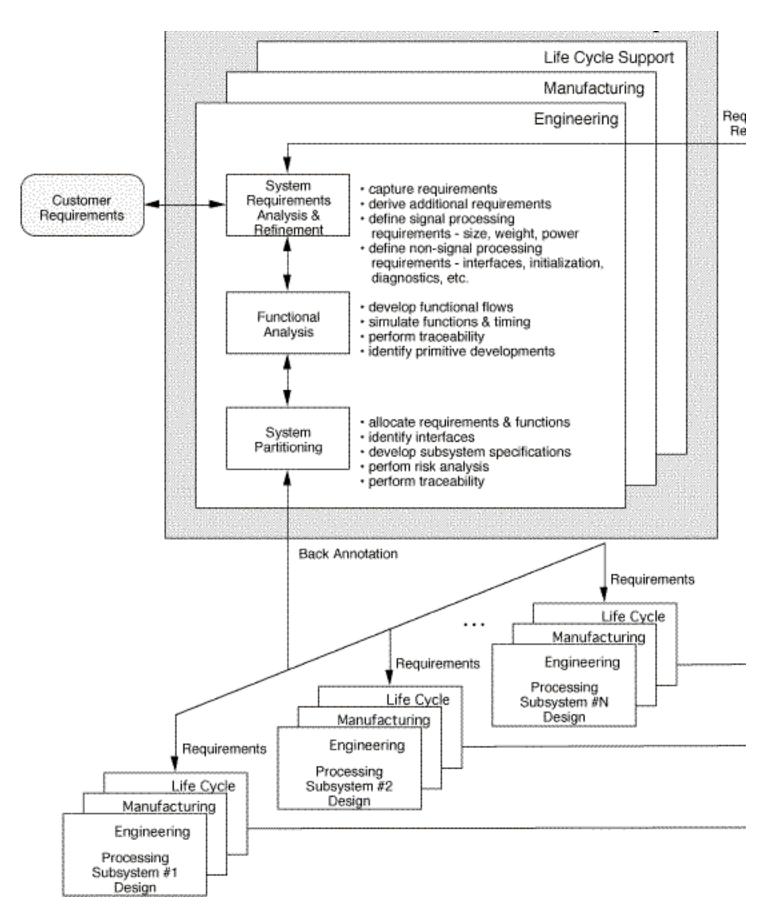

## 5.3 Systems Design Process

The system process captures customer requirements and converts these system-level needs into processing requirements (functional and performance). Functional and performance analyses are performed to properly decompose the system-level description. The system process has no notion of either hardware versus software functionality or processor implementation.

The first major cycle of the spiral shown in Figure 4 - 1 results in a requirements specification that was captured in an appropriate tool; it is the first instantiation of a virtual prototype (VP0). This information is then translated into simulatable functions, which we refer to on RASSP as an **executable specification.** This cycle represents the first level at which requirements are specified so that we can readily match with simulators to verify performance and functionality in an automated manner. In this phase, processing time is allocated to functions and functional behavior is defined in the form of executable algorithms. At this point, all signal processing functions are implementation-independent. High-risk items can spawn prototype analysis and development efforts in a mini-spiral. The executable specification represents a major portion of the systems design information model. This process results in a System Definition Review (SDR) based upon VP0.

A major portion of the systems behavioral definition is in terms of algorithmic functionality. Generating an executable version of the algorithms using systems-level tools is part of the systems effort. In addition, the detailed specification of all messages that must be passed to and from the signal processor must be generated, along with the definition of all required mode transitions.

Click on Section 6.0 to go to a more detailed description of the System Process.

Click on System Process Application Note to go to the application note that not only discusses the methodology but also the use of the Integrated System Engineering tool environment.

Click on System Design to go to the IDEF3X chart for this effort.

#### 5.4 Architecture Design Process Overview

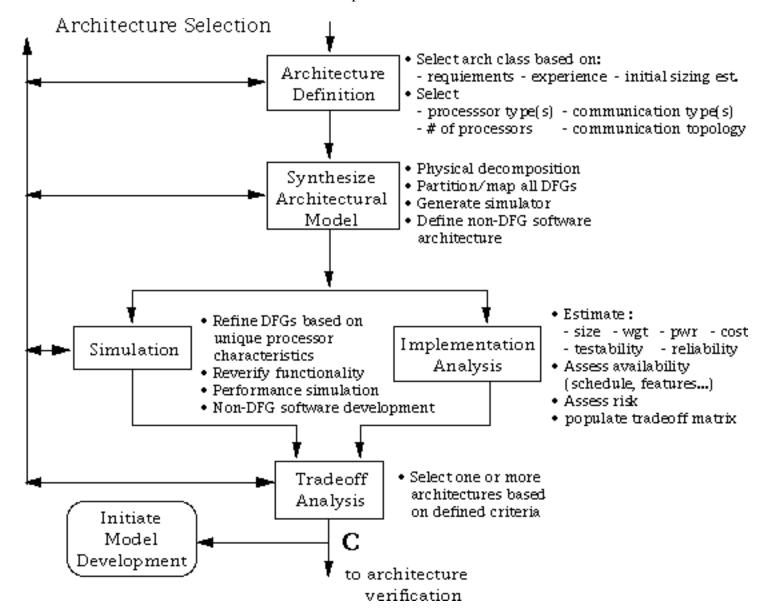

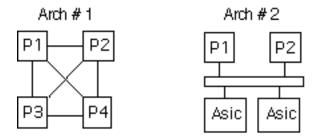

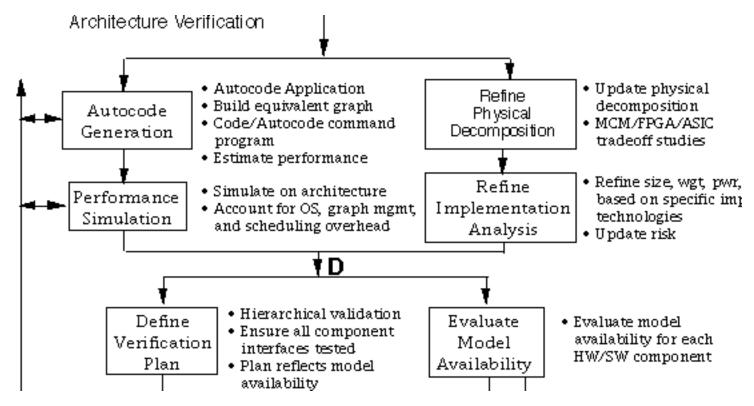

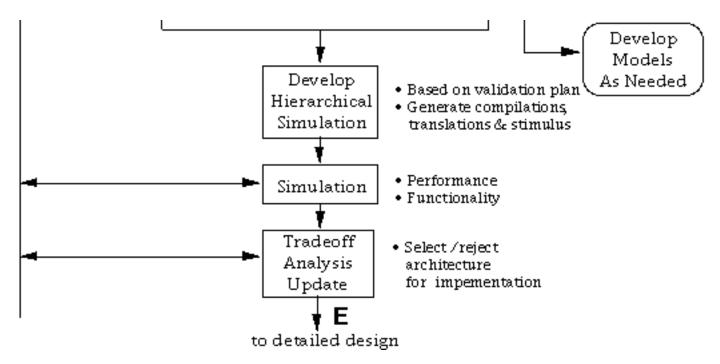

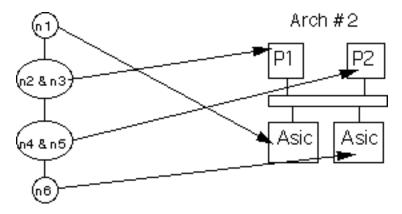

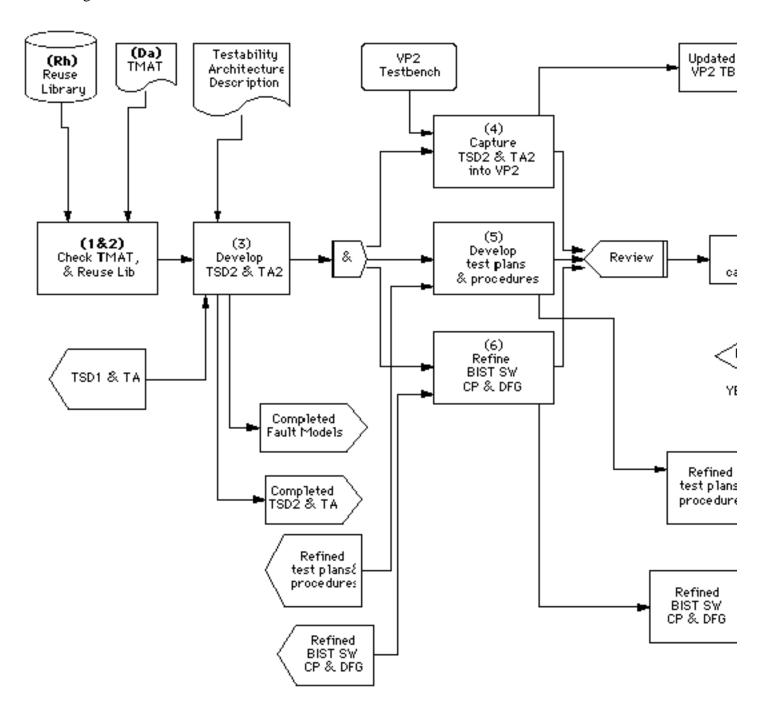

The architecture design process is broken into functional design, architecture selection, and architecture verification. During functional design, initial performance analysis is conducted based upon the processing flows and requirements flowed down from the systems design process. Processing flows are converted to detailed data-flow graphs based upon reuse library primitives. Non-DFG software requirements and tasks are identified. The architecture selection process transforms processing requirements into a candidate architecture of hardware and software elements. This process, which corresponds to the second virtual prototype iteration (VP1) of the signal processor system, initiates the trade-offs between the different processor architecture alternatives. During this process, the system-level processing requirements are allocated to hardware and/or software functions. A non-DFG software architecture is defined, if necessary, and initial software development is begun. The hardware and software functions are verified with each other via co-verification at all steps. The architecture verification process, corresponding to the next virtual prototype (VP2), results in a detailed behavioral description of the processor hardware and definition of the software required for each processor in the system. The intent is to verify all the code during this portion of the design to ensure hardware/ software interoperability early in the design process.

The architecture design process is a new hardware/software codesign processin the RASSP methodology for high-level virtual prototyping and simulation. Traditionally, the architecture definition has been performed partially in the systems design and partially in the hardware design. RASSP has redefined the major processes by product maturity versus functional area into systems, architecture, and detailed design. Hardware/Software codesign encompasses architecture and detailed design. The primary concern in the architecture design process is to select and verify an architecture for the signal processor that satisfies the requirements passed down from the systems definition process. Although the architecture must include everything required in the signal processor, including any control processors which may be required, this discussion focuses on the approach to defining the number and connectivity of the signal processors required to meet the processing requirements. The overall task is to:

- Define and evaluate various architectures

- Select one or more for detailed evaluation that appear to meet the requirements

- Validate the chosen architecture(s) for both function and performance before detailed design

Concurrently, each selected architecture is evaluated for size, weight, power, cost, schedule, testability, reliability, etc. so that a more informed assessment can be made. Software and architecture performance is simulated concurrently so that software performance has a direct impact on the selection of an architecture. This direct coupling through co-simulation immediately inhibits any inclination to design the hardware and make the software fit later.

The architecture design process is library based and Data Flow Graph (DFG) driven. Reuse of both architecture elements and software primitives significantly shortens the design cycle. Candidate architectures are constructed from library models. The signal processing software is then partitioned and mapped to the each candidate architecture. A VHDL simulation for the architecture is also constructed and then simulated to estimate performance. Processor behavioral and performance simulations support trade-offs. Mixed levels of simulation (algorithm, abstract behavioral, performance, ISA, RTL, etc.) are used to verify interaction of the

hardware and software. These models are largely hierarchical VHDL models of the architecture. We choose the models, to the maximum extent possible, from the Model Year Architecture elements in the reuse library. The design team develops and inserts new required library elements into the reuse library to support this design phase. The executable specification has now evolved into a more detailed set of functional and performance models that are architecture-specific. Software algorithm implementations are also now specific to the candidate architecture(s). We conduct an Architecture Design Review based on VP1 and VP2 when the architectural trades are completed and the design has been verified to a high degree of confidence. This process is iterated at the high level to achieve one or more satisfactory designs.

The process is supported by an integrated set of tools to foster iterative design and risk reduction. This results in a more detailed evaluation of architectures (from all perspectives ) at the early stages of design, which eliminates the false starts that are costly later in the design cycle.

At the conclusion of the systems/subsystems process, a processing requirements specification (both functional and performance) that describes the signal processing functionality is provided. Included in these requirements is a description of all the required interfaces between the signal processor and the outside world, such as mode transition requests, signal processing parameter observation and/or parameter setting, and I/O initiation or termination requests. All requirements flowed down from the systems processare traceable throughout the architecture definition process. Candidate architectures are evaluated against these requirements during the hardware/software codesign process. Updated values of the requirements metrics for candidate architectures are passed back to the systems process. In the event that the requirements cannot be met, additional trades are conducted at the systems level. Note that these inputs to the architecture definition process are completely independent of architecture/processor implementation. It is the objective of the architecture process to transform these processing requirements into candidate architectures and to select and verify an implementation approach.

The architecture design process transforms processing requirements into a candidate architecture of hardware and software elements, through hardware/software codesign and co-verification at all steps. As such, the architecture design process incorporates both hardware and software aspects. This results in a detailed behavioral description of the processor hardware and the appropriate software required to verify these descriptions. In addition, this portion of the process also develops and verifies the implementation-specific portions of both the application (algorithm) and control/support software.

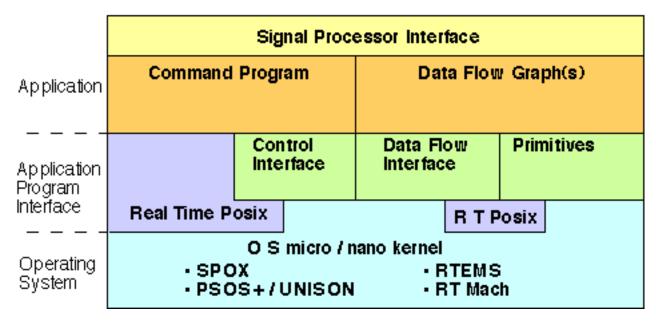

The software portion of the architecture process deviates significantly from traditional (functional decomposition 2167A) approaches. The partitioned software functionality can be broken into four major areas:

- 1. algorithm, as specified in a data flow graph (see Data Flow Graph Design application note)

- 2. scheduling, communications, and execution, as specified by mapping the graph to a specific architecture

- 3. general command/control software (see Autocoding for DSP Control application note)

- 4. other non-DFG based software, i.e. operating system, board support package, etc.

The intent of RASSP is to automate the first three to the maximum extent possible. This will be accomplished using a graph-based programming approach(es) that supports correct-by-construction software development based on algorithm and architecture-specific support library elements. The execution control of these graphs is provided by a run-time system that provides reusable data flow control, which extends the notion of reuse beyond signal processing primitives.

The general command/control software development (see Autocoding for DSP Control application note) will use emerging, object-oriented code development, documentation, and verification tools. The command program interfaces with the outside world via a messaging system and translates messages into graph and I/O control commands for execution by the run-time system. We design all the non-data flow graph software required for the signal processor during the architecture process. We functionally simulate the joint operation of graph-based and non-graph based software to validate the proper interaction of the command program with the data flow graph execution.

As part of the RASSP methodology, as much design, costing, testing, and manufacturing information as possible will be used throughout the architecture design process through concurrent engineering that is supported by tool integrations and design advisors which cover a wide range of disciplines. The architecture process supports a more formalized trade-off process in which all these disciplines provide valuable inputs.

Click on Section 7.0 to go to a more detailed description of the Architecture Design Process.

Click on Hardware/Software Codesign Application Note to go to the application note that describes the latest developments in this process as well as the use of the integrated architecture toolset. This will also provide links to more detailed application notes that describe the use of the various technologies involved with this process. These links are also listed below and will be found throughout the detailed discussion in Section 7.0

- Autocoding for DSP Control

- Data Flow Graph Design

- Design-for-Test

- Token-Based Performance Modeling

- Virtual Prototyping

Click on Architecture Definition to go to the IDEF3X chart for this effort.

### 5.5 Detailed Design Process

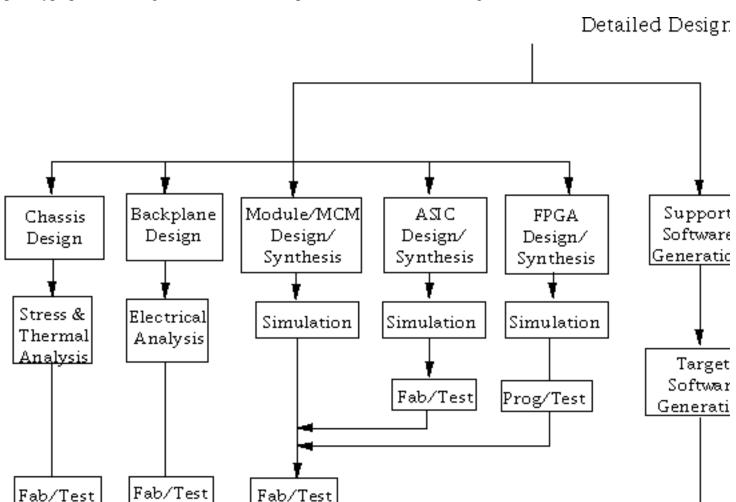

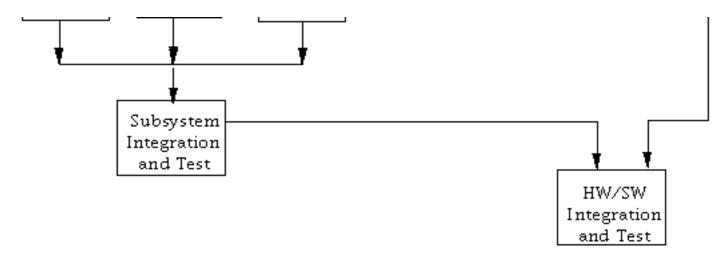

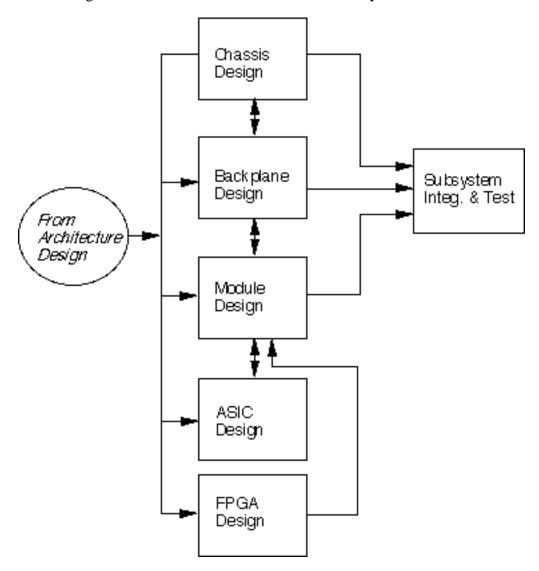

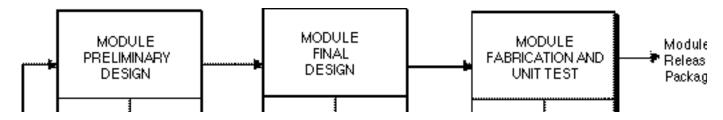

The main objective of the detailed design process is to transform the architectural description of the design into the detailed hardware and software components that we will develop, manufacture, and integrate into a prototype processor. Figure 5 - 2 shows the top-level view of detailed design.

Figure 5 - 2: Detailed Design Process

We partition and develop designs at the behavioral-level (RTL or higher) for processor-level nodes to the appropriate level for all necessary components. This includes ASIC, MCM, and board-level designs, as well as backplane/chassis designs. The process incorporates mechanical and manufacturing elements to ensure that designs meet all specifications for the particular applications. From an industry standpoint, the detailed design process is the most mature area of design, and the improvements on RASSP are optimizations to support rapid prototyping. Toward this end, the process heavily favors two areas:

- Design reuse of validated elements from the RASSP component library to minimize detailed design time

- Synthesis of chip and board-level components from the component libraries.

In the case of software, we must generate any support code that is target specific for the signal processor that has not been completed. This includes initialization, bootup, diagnostics, test software, and any support software required for integration and test which is not part of the operational software. All the software is compiled and verified (to the extent possible) on the final virtual prototype before the detailed design review.

Like the architecture process, this portion of the methodology supports hardware/software codesign, as these elements are fully verified together on the virtual prototype up until the design is released to manufacturing. This virtual prototype iteration (VP3) involves the detailed design of software and hardware elements. As with the prior processes, we design and verify both hardware and software via a set of detailed functional and performance simulations. When this process is completed, the design is established, resulting in a fully verified virtual prototype of the system. We revalidate software that was verified during architecture verification as we develop more detailed models for any of the components. This process provides continual verification as the designs progress toward physical hardware. The transition of these designs to manufacturing is supported by the RASSP enterprise system to provide electronic linking capabilities supporting both concurrent interaction between design and manufacturing, and direct transfer of designs to manufacturing sites.

During the hardware portion of the detailed design process, we transform behavioral specifications of the processor into detailed designs (RTL and/or logic-level) through a combination of hardware partitioning, parts selection, and synthesis. Detailed designs are functionally verified using integrated simulators, and performance/timing is also verified to ensure proper performance. The process results in detailed hardware layouts and artwork, net lists, and test vectors that can then be seamlessly transitioned to manufacturing and test via format conversion of the data. We generate the entire design package required for release to manufacturing for the Detailed Design Review based on VP3, which corresponds closely to today's Critical Design Reviews (CDRs).

At the top level, the detailed design process for hardware is, for the most part, the same for boards, MCM, ASICs, etc. However, at the lower levels, these designs are quite different and use different tools. The

hardware process is partitioned as a function of the hardware element, e.g., chassis, backplane, board, chip, etc.