# Timer User's Guide

V6.1

### Actel Corporation, Mountain View, CA 94043

© 2004 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 502-9123-5/10.04

Release: October 2004

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### **Trademarks**

Actel and the Actel logotype are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

Mentor Graphics, Precision RTL, Exemplar Spectrum, and Leonoardo Spectrum are registered trademarks of Mentor Graphics, Inc.

WaveFormerLite is a registered trademark of SynaptiCAD, Inc.

Synplify is a registered trademark of Synplicity, Inc.

Sun and Sun Workstation, SunOS, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc

Synopsys is a registered trademark of Synopsys, Inc.

Verilog is a registered trademark of Open Verilog International.

Viewlogic, ViewSim, ViewDraw and SpeedWave are trademarks or registered trademarks of Viewlogic Systems, Inc.

Windows is a registered trademark and Windows NT is a trademark of

Microsoft Corporation in the U.S. and other countries.

UNIX is a registered trademark of X/Open Company Limited.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

# **Table of Contents**

| Timer                                                                                                                | 7  |

|----------------------------------------------------------------------------------------------------------------------|----|

| Welcome to Timer                                                                                                     | 7  |

| Timer user interface                                                                                                 | 7  |

| Timer Toolbar                                                                                                        | 7  |

| Status Bar                                                                                                           | 8  |

| Summary tab                                                                                                          | 8  |

| Timer Expanded Path window                                                                                           | 10 |

| Clocks tab                                                                                                           | 11 |

| Paths tab                                                                                                            | 11 |

| From All Inputs To All Registers / CLK                                                                               | 12 |

| From All Registers / CLK To All Registers / CLK                                                                      | 12 |

| From All Registers / CLK To All Outputs                                                                              | 12 |

| All Inputs To All Outputs                                                                                            | 12 |

| Breaks tab                                                                                                           | 13 |

| Timer Preferences                                                                                                    | 13 |

| Maximum List Size                                                                                                    | 13 |

| Minimum Delay / Maximum Delay: Enables you to filter paths for values above, between, or below the specified values. |    |

| Timer Menu Commands                                                                                                  | 14 |

| File Menu                                                                                                            | 14 |

| Edit Menu                                                                                                            | 14 |

| Tool Menu                                                                                                            | 15 |

| Help Menu                                                                                                            | 15 |

| Timing report dialog box                                                                                             | 15 |

| Using Timer                                             | 15                           |

|---------------------------------------------------------|------------------------------|

| Determining your clock frequency                        | 15                           |

| Adding and Removing Break Points                        | 16                           |

| Setting Preferences in Timer                            | 17                           |

| Delay preferences                                       | 17                           |

| Changing and displaying paths                           | 18                           |

| Displaying the Shortest Paths First                     | 19                           |

| Delay filters (max. or min.) / Sorting by actual or sla | ack delays19                 |

| Setting Minimum or Maximum Delay Filters                | 19                           |

| Sorting and Displaying by Actual or Slack Delays        | 19                           |

| Displaying by Actual Delay                              | 20                           |

| Displaying by Slack Delay                               | 20                           |

| Best\Typical\Worst Case Analysis                        | 20                           |

| Selecting paths - Adding or removing break paths        | 20                           |

| Adding and Removing Break Paths                         | 21                           |

| Timer Tcl Preferences                                   | 21                           |

| Path Analysis                                           | 21                           |

| Path Analysis                                           | Error! Bookmark not defined. |

| Display paths                                           | 21                           |

| Expanding paths                                         | 22                           |

| Clock Skew Analysis                                     | 25                           |

| Adding Path Sets                                        | 26                           |

| Adding path sets                                        | Error! Bookmark not defined. |

| Add a "one input to all outputs" path set               | 28                           |

| Add an "all inputs to one output" path set | 28 |

|--------------------------------------------|----|

| Edit or Remove a Path Set                  | 28 |

| Adding/Removing sets with keywords         | 28 |

| Timing Constraints                         | 30 |

| Specifying timing constraints              | 30 |

| Constraint guidelines                      | 30 |

| Delay Constraint Guidelines                |    |

| General Guidelines                         | 30 |

| Specifying clock constraints               | 31 |

| Clock exceptions                           | 31 |

| Path constraints - specifying or removing  | 32 |

| Removing Constraints                       | 32 |

| Timing Results                             | 32 |

| Export Results                             | 32 |

| Commit before you exit                     | 32 |

| Generate reports                           | 33 |

| Violations Report                          | 33 |

| Keyword Filters                            | 34 |

| Keywords                                   | 34 |

| Levels of Keywords                         | 34 |

| Filtering                                  | 34 |

| Functions                                  | 34 |

| Supported Keywords                         | 34 |

| First-Level Keywords                       | 35 |

| Second-Level Keywords                   | 35 |

|-----------------------------------------|----|

| Second-Level Exceptions                 | 36 |

| Calculating Delays                      | 37 |

| Delays, PLLs, RAMs, and FIFOs           | 37 |

| PLLs                                    | 37 |

| PLLs for Axcelerator                    | 38 |

| RAMs and FIFOs                          | 38 |

| Using ChipPlanner/ChipEditor with Timer | 38 |

| Timing delay constraint definitions     | 40 |

| DTL Terminals                           | 40 |

| Signal Path                             | 40 |

| Network                                 | 40 |

| Path Delay                              | 40 |

| Delay Constraint                        | 40 |

| Don't Care Path                         | 40 |

| Global Stop                             | 40 |

| Clock Exception                         | 40 |

| Timer Glossary of Terms                 | 40 |

| clock exception                         | 41 |

| critical path                           | 41 |

| delay constraint                        | 41 |

| destination                             | 41 |

| don't care path                         | 41 |

| Dynamic Timing Analysis                 | 41 |

| filter                                  | 41 |

| global Stop                             | 41 |

| network                      | 41 |

|------------------------------|----|

| path                         | 41 |

| path delay                   | 42 |

| path sets                    | 42 |

| signal path                  | 42 |

| slack                        | 42 |

| Standard Delay Format (SDF)  | 42 |

| Static Timing Analysis (STA) | 42 |

| status bar                   | 42 |

| toggle rate                  | 42 |

| Contacting Actel             | 42 |

| Actel Headquarters           | 42 |

| Technical Support            | 43 |

| Visit Tech Support Online    | 43 |

| Contacting Technical Support | 43 |

| Customer Service             | 43 |

| UNIX help known issues       | 44 |

| Index                        | 45 |

Timer Toolbar

Timer

### **Timer**

## Welcome to Timer

Timer is Actel's static timing analysis tool. Timing analysis is a convenient and thorough method of analyzing, debugging, and validating the timing performance of a design. This is achieved by breaking down the design into sets of paths. Delays for each path are then calculated and every path is checked for timing violations.

You can only use Timer after you open a compiled design (\*.adb file), or after compiling a netlist in designer. If you invoke Timer before compiling your netlist, Designer guides you through the compile process.

There are three ways to start Timer:

- Choose **Timer** from the **Tools** menu.

- Click the **Timer** icon in Designer's toolbar.

- Click the **Timer** button in Designer's design flow.

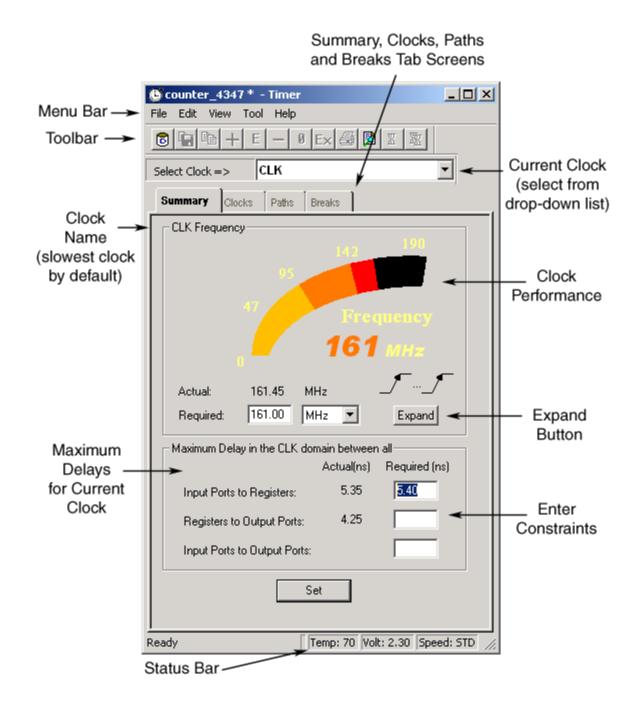

### Timer user interface

Timer's four tab screens organize and display static timing information according to the timing analysis preferences you set in the <a href="Preferences">Preferences</a> dialog box.

Timer consists of four tab screens: <u>Summary</u>, <u>Clocks</u>, <u>Paths</u>, and <u>Breaks</u> (Timer does not display the <u>Clocks</u> tab screen if the device you are using has no clock).

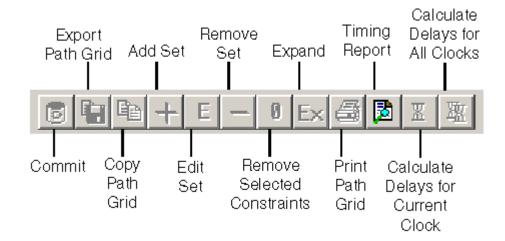

### **Timer Toolbar**

The Timer toolbar contains commands for performing common Timer operations on your designs. Tool tips are available for each button.

Timer Toolbar

Summary tab Timer Toolbar

#### **Status Bar**

Timer's status bar displays information on menu commands, error messages, your selected temperature, voltage, and speed grade. In addition, Timer displays the following:

- Temp: Displays the temperature consistent with the operating conditions selected.

- **Volt:** Displays the voltage consistent with the operating conditions selected.

- Speed Grade: Displays the speed grade of the selected device.

# **Summary tab**

By default, Timer's **Summary** tab screen displays the maximum frequency for the current clock selected in the **Select Clock** drop-down list box. You may need to specify false path or multi-cycle path constraints in order to obtain the correct frequency for your selected clock.

Timer Toolbar Summary tab

Timer Summary Tab Screen - PC Only

To change the default clock, select the clock from the clock list.

Click the **Expand** button in Timer **Summary** tab to display the details of the path that determined the maximum clock frequency in the **Expanded Path window**.

The icon above the **Expand** button shows the edges of the clock source triggering the two registers delimiting the critical path (the path responsible for the clock frequency). The icon represents four possible configurations: Rising-Rising, Rising-Falling, Falling-Rising, and Falling-Falling. The figure above shows the Rising-Rising configuration.

The Summary tab displays the actual longest/shortest delay between all Input Ports to Registers, Registers to Output Ports, and Input Ports to Output Ports.

Enter your new delay values in the **Required** input boxes and click **Set** to recalculate your delays.

**Note:** If you add constraints to the set of paths listed in this tab, Timer uses them as global constraints for that clock. When you apply constraints in the Summary tab, it is easy to over-constrain the design; this may degrade the quality of the Timing-Driven Layout and increase the overall run time.

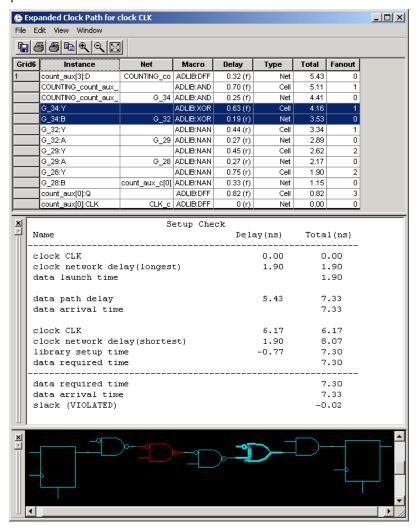

# **Timer Expanded Path window**

The Expanded Paths window is comprised of three components:

**Expanded Paths Grid** - Shows all delay components for the selected path (Instance, Net, Macro, Delay, Type, Total Delay and Fanout details). For Delay, (r) stands for rising edge and (f) for falling edge. If you expand a register to register path, the **Expanded Path** window displays relevant register setup timing information. Click a component to select the corresponding element in the schematic.

Setup Check / Hold Check window - Set the Show option (in Preferences) to Longest to view a detailed analysis of the Setup Check. Set the Show option to Shortest to view a detailed analysis of the Hold Check. (These analyses include clock insertion delay information.)

Expanded Paths Schematic - Displays a schematic view of the expanded path.

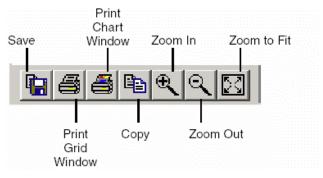

The Expanded Path window includes a toolbar that enables you to Save, Print, Copy, and Zoom in the schematic.

Timer Expanded Path Toolbar

Save: Save the contents of the Grid as a .txt file

**Print Grid Window:** Print the contents of the Grid window **Print Chart Window:** Print the contents of the Chart window

Copy (Grid to Clipboard): Copy the contents of the Grid window to the clipboard

Zoom In: Click to zoom in on the Chart window

Zoom Out: Click to zoom out on the Chart window

Zoom to Fit: Click the Zoom to Fit button to automatically fit the entire path in the Chart window

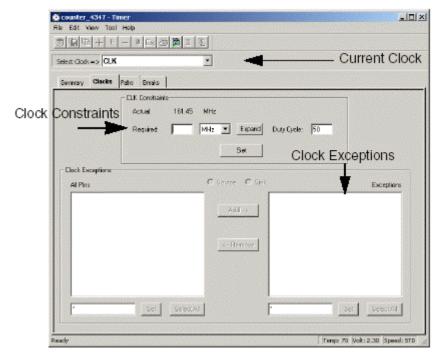

Clocks tab

**Note:** The expanded paths window for eX, SX-A, Axcelerator, and Flash devices shows the expanded path on a pin-to-pin basis rather than an input-to-input basis. There is a separation between the module delay and the net delay.

Anything you select in the Expanded Paths grid or Schematic window is reflected in both windows.

# Clocks tab

The Clocks tab allows you to enter constraint information and set clock exceptions. Select the default clock from the Select Clocks list.

Clocks Tab

Enter constraint information in the Constraints area and click Set.

Clock exceptions are terminals in a synchronous network that should be excluded from the specified clock analysis. This is useful for multi-cycle paths.

If you specify a pin in **Clock Exceptions**, Timer excludes them from Input to Register, Register to Register, and Register to Out calculations. You may add the path that travels through the excluded pin manually and then apply the proper constraints in the <u>Paths</u> tab.

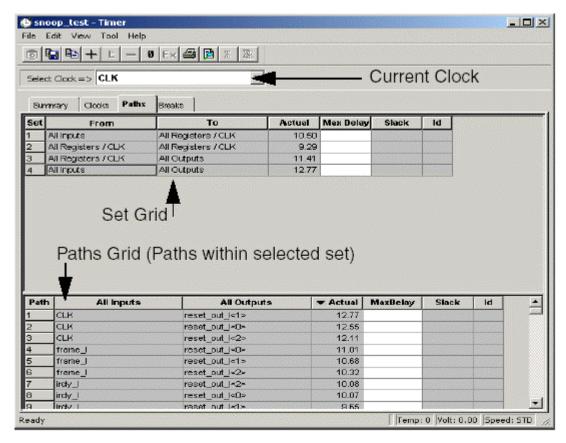

# Paths tab

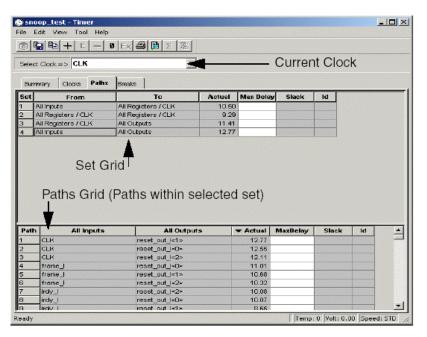

The **Paths** tab displays timing analysis information for categories of paths, known as "sets," and the paths within each set. The **Paths** tab displays the sets in the set spreadsheet (at top) and the paths within each set (at bottom).

Paths Tab

The Paths tab default setting displays four path sets:

### From All Inputs To All Registers / CLK

Displays all paths from the input ports of the design to the synchronous input pins of all the registers in the current clock domain. In this instance, CLK is an example of the current clock domain.

### From All Registers / CLK To All Registers / CLK

Displays all paths from the clock pin of registers in the current clock domain to the synchronous input pins of all the registers in the current clock domain; in this instance, CLK is an example of the current clock domain. To view the register setup and clock skew, right-click the desired path in the paths grid and select **Expand Path** from the context menu, or click the **Expand Path** button.

To view the Hold time (instead of the Setup time), change your setting in the Timer Preferences, Changing and Displaying paths.

### From All Registers / CLK To All Outputs

Displays all paths from the clock pin of registers in the current clock domain to the primary outputs of the design.

### **All Inputs To All Outputs**

Displays all input ports to all output ports in the design. This set is completely asynchronous (independent of the clock).

All the sets default to display the longest path in the category. You can change this default setting by selecting Preferences from the

**File** menu. When you select a set, Timer displays the paths within the set in the lower spreadsheet labeled "Paths." The spreadsheet displays a sorted list of paths (the number of paths it displays is controlled in the Preferences dialog box). Double-click the column headings to sort the columns.

**Note:** The runtime required to compute the content of the spreadsheet is a function of the number of paths you wish to display. Select Preferences from the File menu to change the default settings.

Breaks tab

The timing information displayed for sets and paths includes:

- Actual: The actual delay calculated by Timer for each path. Timer does not include setup time and destination register data when calculating the Actual delay.

- Max Delay: The maximum required delay specified. Do not interpret this value as the clock frequency. To set clock frequency, input on the Summary tab, or on the Clocks tab. Timer includes setup time and skew when calculating Max Delay.

- Slack: The difference between the maximum required delay and the actual delay.

- **ID:** The constraint ID for the path.

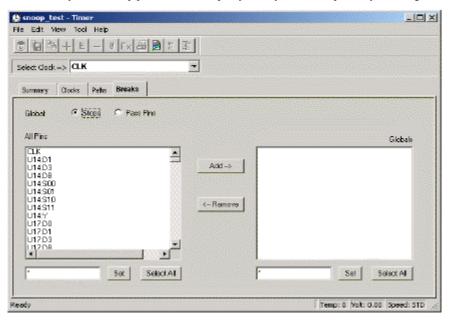

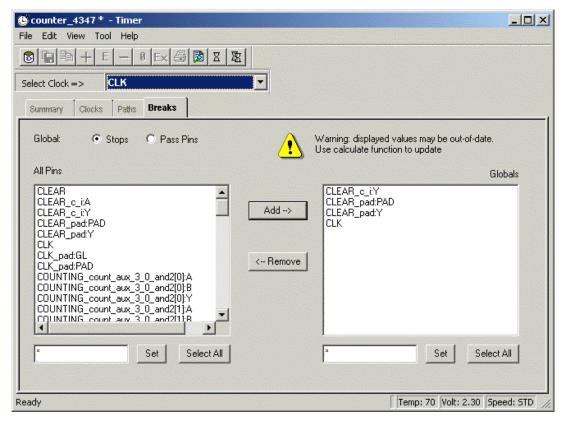

## **Breaks** tab

Use the **Breaks** tab to enter global stops and pass pins. A global stop is a defined intermediate point in a network that forces all paths through the defined point to be "don't care" paths regardless of any constraint assignment. Setting a pass pin on a module pin enables you to see a path through individual pins, which you are not normally allowed to view a path through.

Note: If you are not careful when you set a stop pin on a module pin, you may set a false path in your design.

Breaks Tab

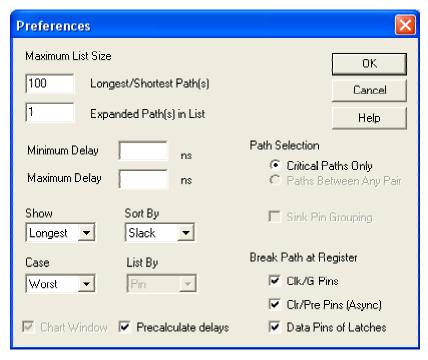

# **Timer Preferences**

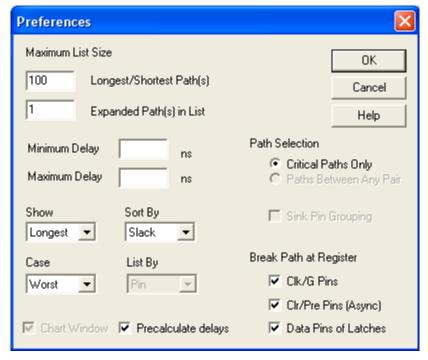

The Timer Preferences dialog box enables you to control and filter the way that Timer reports timing results.

#### **Maximum List Size**

Longest/Shortest Paths: Defines the maximum number of paths listed in the Expanded Paths window and the Paths tab.

Expanded Paths in List: Determines the number of paths that will be shown in the expanded window for two end points (terminals).

Timer Menu CommandsMinimum Delay / Maximum Delay: Enables you to filter paths for values above, between, or below the specified values.

# Minimum Delay / Maximum Delay: Enables you to filter paths for values above, between, or below the specified values.

Show: Defines which paths Timer displays (longest or shortest). Note that the paths Timer displays are related to Setup and Hold Check times. When Timer displays paths from longest to shortest, it reports setup times for registers. To view hold times in the **Expanded Path** window, you must set the **Preferences** to show the **Shortest** paths.

<u>Sort By</u>: Displays and sorts timing results according to Actual or Slack delays. Slack delay values are the difference between (user-specified) constraints and actual delays. If you select **Sort By Slack** and do not specify a constraint, Timer sorts by slack using the delay of critical path.

<u>Case</u>: Sets your operating condition preferences. View the operating conditions for each case in **File** -> **Operating Conditions**.

<u>Path Selection</u>: Select Critical Paths to display the longest path between any two end points (terminals). The Paths Between Any

**Pair** option enables you to evaluate any path between any two end points. The **Paths Between Any Pair** option is disabled for families that use the pin-to-pin timing model.

Break Path at Register: Clear the check boxes in Break Path at Register to display paths that pass through (and do not "break") at all Clock, Clear, Gate, and Preset pins. Clear the CLR pin check box to get the clk-to-out delay.

### Timer Menu Commands

The PC and workstation versions of Timer have the same menus. However, some dialog boxes may look slightly different on the two platforms due to the different window environments. The functionality is the same on both platforms, though the locations of the fields and buttons on the dialog boxes may vary. The names of some fields may also vary between the PC and workstation versions.

#### File Menu

Commit: Commits timing information to Designer

**Export Set Grid:** Exports selected cells in the sets grid to a file **Export Path Grid:** Exports selected cells in the path grid to a file

Print Set Grid: Prints selected cells in the sets gridPrint Path Grid: Prints selected cells in the paths grid

**Operating Conditions:** Displays the operating conditions Timer uses to calculate delays. Operating conditions change depending on your Worst, Typical, or Best case selection in the <u>Preferences</u> dialog box.

Preferences: Invokes Preferences dialog box, where you can set analysis and display preferences

Close: Closes Timer

#### **Edit Menu**

Copy Set Grid: Copies set grid to clipboard

Copy Path Grid: Copies path grid to clipboard

Remove Selected Constraints: Removes selected constraints, not all

Remove All Constraints: Removes all constraints in Timer

Expand Paths: Expands path in new window

Add Set of Paths: Defines and adds new path set to Paths tab

Edit Set of Paths: Edit added path set

Remove Set of Paths: Removes added path sets

#### **Tool Menu**

Report Paths: Generates Timing report

**Report Violations:** Generates a Timing report, timing violations only

Calculate delays: Calculates delays for the current clock

Calculate all delays: Calculates delays for all clocks and selects the worst (clock with greatest delay)

#### **Help Menu**

**Help Topics:** Lists of Help Topics

Reference Manuals: Opens Timer's User's Guide

# Timing report dialog box

**External Setup-hold Timing Check:** Selecting the **External Setup hold** timing check box adds specific sections to the timing report, including External setup and hold as well as clock-to-out timing information.

**Slack Threshold (ns):** Sets the maximum slack threshold for all the paths included in the report. Use this value in conjunction with the **Sort by: Slack** option in the Timer <u>Preferences</u> dialog box.

**Sort by slack (in Preferences):** If you select **Sort By Slack** in the **Preferences** dialog box, you can also limit the number of paths displayed based upon the Slack threshold.

For example, if you want to see only the paths that have a slack less than 5 ns, select **Slack** in the **Sort by** drop-down list box in the **Preferences** dialog box and then enter 5 in the **Slack Threshold** text box in the **Timing Report** dialog box. The timing report displays all the timing paths that have a slack of 5 ns or less (that is, all paths that met the timing constraints by  $\leq$ 5 ns as well as all the paths that failed to meet constraints).

If you wish to display the timing paths that failed by 10 ns or more, enter -10 in the **Slack Threshold** box; the timing report displays the paths that failed to meet the timing constraints by 10 ns or more.

# **Using Timer**

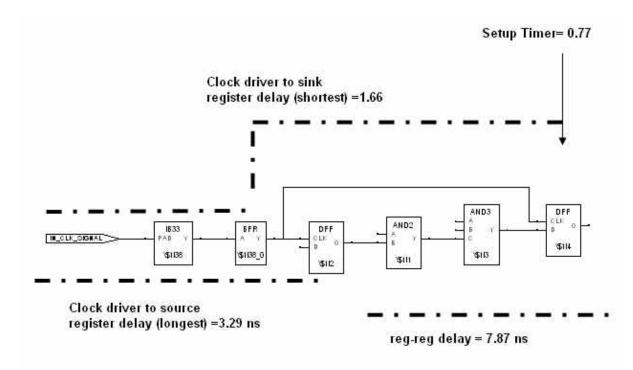

### **Determining your clock frequency**

Because a design's performance is often measured by the clock frequency, determining the clock frequency is the most common use of static timing analysis.

### To obtain a specific clock frequency:

- 1. Click the **Summary** tab in the **Timer** window.

- 2. Select a clock from the **Select Clock** list. The selected clock becomes your current clock. The frequency is displayed under the speedometer.

The clocks listed in the drop-down menu are defined as signals which drive the clock or gated input of two or more adjacent registers. For pin-to-pin delay families, one register is enough to have the clock listed as a potential clock. Timer does not support virtual clocks.

In frequency calculations, values for latency is assumed to be 0, the duty cycle is 50%, and the starting clock edge is rising. (You can set the duty cycle in the Clocks tab.) For pin-to-pin timing model families, Timer takes into account the register setup and the clock skew when estimating the maximum clock frequency. For more information on calculating delays, refer to <u>Calculating Delays</u>.

Clock frequency should be the inverse of reg-reg delay plus setup time. However, this is not true with clock skew.

For pin-to-pin timing model families (54SX-A, eX, Axcelerator, and ProASIC, ProASIC PLUS, and ProASIC3/E), Timer takes into account the register setup and the clock skew when estimating the maximum clock frequency.

Your clock frequency is: 1 / (path delay + setup - skew) if both registers are sensitive to the same clock edge.

### **Adding and Removing Break Points**

The Timer default behavior is to break paths at clocks. You can change this default behavior in the Timer Preferences dialog box. Without stop points (or break points), Timer reports all the paths from pad to pad in the design. If you do not want to see the paths going through registers clock pins, you can specify these as break points. The path running through those pins is not displayed.

Setting a pass on a module pin enables you to see a path through individual pins. Additionally, you can set a global pass on all Clk/G and Clr/Pre pins in the <u>Preferences</u> dialog box, which is available by choosing **Preferences** from the **File** menu.

#### To add break points:

- 1. Click the Breaks tab.

- 2. Select Global Stops or Pass Pins. The All Pins list box displays the pins.

- 3. Select the pin(s). The **All Pins** list box defaults to show all pins. Text boxes are provided below the list boxes to help you limit the list for consideration. Enter a value and click **Set**. The \* character is used as a wildcard. To select multiple pins, hold down the **CTRL** key while selecting with your mouse. Click **Select All** to select all pins displayed in the **All Pins** list box.

- 4. Click **Add**. The **Stops** or **Pass Pins** will be added to the **Global** list box as break points.

Breaks Tab - Stops Selected

#### To remove break points:

- Click the **Breaks** tab.

- Select Global Stops or Pass Pins. The break points are displayed in the Global list box.

- Select break Points to remove. To select multiple breaks, hold down the CTRL key while selecting with your mouse. Click Select All to select everything displayed in the Global list box.

- Click **Remove**. The pin(s) will be removed from the **Global** list box.

# **Setting Preferences in Timer**

### **Delay preferences**

The Preferences dialog box controls your delay and timing analysis preferences. If you are using Tcl, consult the Tcl Command Summary for a list of the commands related to preferences.

You may wish to prevent Timer from calculating delays when the tool starts. (By default, Timer estimates all potential clock frequencies, as well as the delays corresponding to the four primary sets (All Inputs to All Outputs, All Inputs to Registers, Registers to All Outputs, Registers to Registers) associated with the slowest clock when the tool opens.)

Preferences - Precalculate Delays Selected

To change your option for pre-calculating delays, from the File menu, choose Preferences and deselect Precalculate delays.

### **Changing and displaying paths**

Use the **Preferences** dialog box to control the number of paths displayed in the **Paths** tab, **Expanded Paths** window, and **Timing Report**.

To change the number of paths that Timer displays:

- 1. From the **File** menu, choose <u>Preferences</u>. The **Preferences** dialog box appears.

- 2. In the **Maximum List Size** area, enter your default preferences for the maximum number of **Longest/Shortest Path(s)** and **Expanded Path(s)** that you want to display.

The value for **Longest/Shortest Path(s)** is set to 100 by default; you can modify the value if you wish to see more paths in your report. However, the higher the value the longer it takes to invoke Timer.

3. Click OK.

Preferences Dialog Box

## **Displaying the Shortest Paths First**

By default, Timer displays the first 100 paths from longest to shortest in the **Paths** tab and **Expanded Paths** window. When Timer displays paths from longest to shortest, it reports setup times for registers. To view hold times in the **Expanded Path** window, you must set the **Preferences** to **Show** the **Shortest** paths.

#### To display the shortest paths first:

- 1. From the File menu, choose Preferences. The Preferences dialog box appears.

- 2. Select **Shortest** from the **Show** drop-down menu.

- 3. Click OK.

# Delay filters (max. or min.) / Sorting by actual or slack delays

### **Setting Minimum or Maximum Delay Filters**

Use the <u>Preferences</u> dialog box to filter paths for delays above, below, or between a specified value. Enter your display preferences in the **Maximum Delay** and **Minimum Delay** boxes and click **OK**.

# **Sorting and Displaying by Actual or Slack Delays**

Timer can display delay information in two ways:

- Actual delay values

- Slack, which is the difference between actual delay and a user-specified delay (that is, a user-specified constraint)

By default, Timer displays the paths sorted by slack.

**Note:** In case there are no constraints and you select Sort by Slack, Timer sorts the paths based on the criticality. The most critical path is the one that limits the frequency of the design. If the design includes flip-flops triggered by different edges of the clock, the most critical path may not be the path with the longest actual delay.

### **Displaying by Actual Delay**

The actual delay is the path delay between two points in your design. This is the only way to sort your data if you do not have any timing constraints entered (for information on setting timing constraints, see <u>Constraint Guidelines</u>). If you have entered timing

constraints, the actual delay report automatically displays the slack - even if you don't ask for it - but the data will always be listed from longest to shortest actual delay.

Actual delay measurements may be calculated before or after layout.

#### To display Actual delay:

- 1. From the File menu, choose Preferences. This displays the Preferences dialog box

- 2. Select **Actual** in the **Sort By** drop-down menu.

- 3. Click OK.

### **Displaying by Slack Delay**

Slack delay is the delay difference between a timing constraint entered in Timer and the actual delay of a path. For example, if a signal takes 20 ns to get from point A to point B, and you entered a timing constraint of 15 ns, the Timing Report would list -5 ns slack for that path. Thus, if the slack is negative, then the actual delay did not meet the desired timing by the absolute value of the slack (in ns). Conversely, if the slack value is positive, then the timing constraint was met, with the slack value (in ns) to spare. In a violations report, Timer sorts the data (by default) from longest to shortest slack.

When displaying slack, all the paths without timing constraints are filtered from the reported data. This enables you to quickly determine how well your design meets your timing requirements. This is especially useful for viewing critical delays like register-to-register, clock-to-out, and input-to-register.

# Best\Typical\Worst Case Analysis

By default, Timer displays the worst-case analysis.

#### To display the best or typical case analysis:

- 1. From the **File** menu, choose **Preferences**. The **Preferences** dialog box appears.

- 2. Select **Best**, **Typical**, or **Worst** from the **Case** drop-down menu. If you change the setting, timing is recalculated for the entire design; this may take a few minutes.

- 3. Click OK.

# Selecting paths - Adding or removing break paths

Normally, Timer displays only critical paths. Critical paths are the longest paths between any of the starting points (terminals) and each ending terminal. If you would like to see the timing of all paths between any of the starting terminals and any of the ending terminals, select **Paths Between Any Pair** (input-to-input timing model families only) in the **Path Selection** area of the <u>Preferences</u>

dialog box. Selecting Critical Paths displays only critical paths.

### Adding and Removing Break Paths

Asynchronous feedback paths in a design can cause paths to be reported as having excessive delays. The most common example is feedback paths through asynchronous Set or Reset pins to banks of flip-flops, like a state machine or a counter.

#### To exclude paths:

- 1. From the File menu, choose Preferences. The Preferences dialog box appears.

- 2. Break Paths at Register. Choose Clk/G Pins, Clr/Pre Pins (Async) or Data Pins of Latches to prevent displaying paths that pass through either clock, gated, clear, preset, or data pins of flip-flops or latches.

Note: The Break Paths at Register option is selected by default, and the paths are excluded. Clear the check boxes in the Timer Preferences menu to display these paths.

- 3. Click **OK**.

# **Timer Tcl Preferences**

For Tcl users, the summary of commands for Timer is as follows:

```

report -type timer

[-sortby {actual,slack}]

[-maxpaths <num>]

[-case {worst,typical,best}]

[-setup_hold {on,off}]

report name.txt

```

# Path Analysis

Timer organizes and displays data based on your timing analysis <u>preferences</u>. Timer assists you in analyzing critical paths, paths with the greatest delay, and by expanding paths so you can trace delays along paths. The <u>Expanded Path</u> window provides delay information for the path that is in greatest violation.

You can change your preferences to control how you display paths, add path sets, and expand paths.

# Display paths

Path sets (groups) and paths within each set are displayed on the Paths tab. You can create your own sets and add them to the paths tab (see <u>Adding path sets</u>). Also, Timer displays all previously entered sets that have a constraint in the Set grid.

### To display paths:

- 1. Click the **Paths** tab. By default, Timer displays four path sets in the set grid.

- 2. Click a set. Timer displays the paths in the path grid.

Timer Paths Tab

When you set a clock constraint for a pin-to-pin timing model family, it is mapped into specific register-to-register max delay values; these values appear in the max delay of each specific path in the spreadsheet. Timer takes into account register setup and clock skew when computing max delay values for these pin-to-pin model families.

The register-to-register selections are based on the clock domain selected in the <u>Clocks</u> tab. (To specify another clock, select the Select Clock menu from the Toolbar.) See the index for a list of <u>Paths</u> tab information.

All delays shown are worst-case by default. To change this setting, see <u>Case Analysis</u>.

# **Expanding paths**

Each path has one or more logic macros and nets that contribute to its total delay. By expanding the path, you can view detailed delay information for that particular path.

Note: With the exception of parallel edges, parallel paths are not available for families that use the pin-to-pin timing model.

### To expand a path:

- 1. Click the **Paths** tab.

- 2. Select a path set. Paths within that set are displayed in the path grid.

- 3. Select the path you wish to expand.

4. Expand the path by double-clicking the path or right-click and select **Expand Path** from the context menu, or in the **Edit** menu, choose **Expand Path**. The **Expanded Path** window opens and displays a single path in the **Expanded Path Grid** and a graphical representation of the path in the **Schematic Window**.

Timer Expanded Path Window

Clock frequency should be the inverse of reg-reg delay plus setup time. However, this is not true with clock skew.

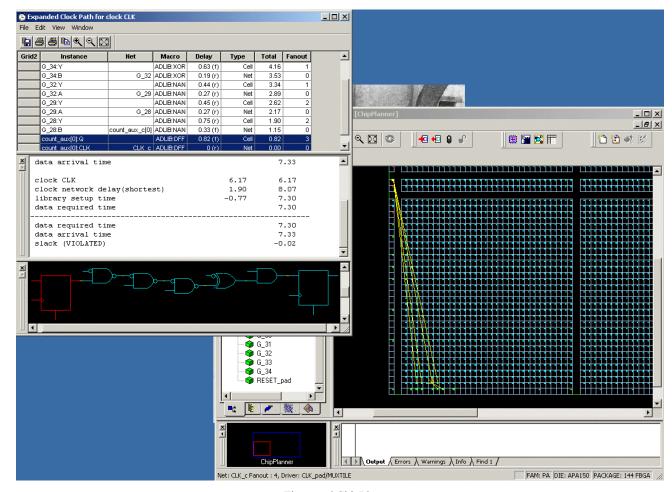

For a pin-to-pin timing model (SX-A, eX, Axcelerator, ProASIC, ProASIC, ProASIC<sup>PLUS</sup>, and ProASIC3/E families), Timer takes into account the register setup and the clock skew (starting in R1-2003) when estimating the maximum clock frequency. However, the setup value is not included in the actual delay reported between the clock pin of a source register and the data pin of a sink register. The Timer Expanded Path window shows Setup Check / Hold Check information. Set the Show option (in Preferences) to Longest to view a detailed analysis of the Setup Check and set the Show option to Shortest to view a detailed analysis of the Hold Check. (These analyses include clock insertion delay information.)

The figures below show the correlation between the Expanded Path Grid (at top), the Setup Check or Hold Check report (at middle) and the Schematic window (at bottom).

**Note:** The values displayed in the Setup Check / Hold Check report are affected by rounding in calculations, so you may see a very slight discrepancy in the difference between the data required time and the data arrival time (the slack time).

| Grid1 | Instance  | Net   | Macro      | Delay    | Туре | Total | Fanout |

|-------|-----------|-------|------------|----------|------|-------|--------|

| 1     | \$1I4:D   | \$1N9 | ADLIB:DFF  | 1.18 (f) | Net  | 7.87  | 0      |

| 3     | \$113:Y   |       | ADLIB: AND | 0.44 (f) | Cell | 6.68  | 1      |

| -     | \$113:C   | \$1N7 | ADLIB: AND | 2.51 (f) | Net  | 6.25  | 0      |

| -     | \$1I1:Y   |       | ADLIB: AND | 0.73 (f) | Cell | 3.74  | 1      |

| -     | \$1I1:B   | \$1N5 | ADLIB: AND | 2.20 (f) | Net  | 3.01  | 0      |

| 3     | \$112:Q   |       | ADLIB:DFF  | 0.82 (f) | Cell | 0.81  | 1      |

| į.    | \$112:CLK | clk1  | ADLIB:DFF  | 0 (r)    | Net  | 0.00  | 0      |

| Setup Chec                    | k         |            |

|-------------------------------|-----------|------------|

| Name                          | Delay(ns) | Total (ns) |

| clock IN CLK SIGNAL           | 0.00      | 0.00       |

| clock network delay(longest)  | 3.29      | 3.29       |

| data launch time              |           | 3.29       |

| data path delay               | 7.87      | 11.16      |

| data arrival time             |           | 11.16      |

| clock IN CLK SIGNAL           | 8.33      | 8.33       |

| clock network delay(shortest) | 1.66      | 9.99       |

| library setup time            | -0.77     | 9.22       |

| data required time            |           | 9.22       |

| data required time            |           | 9.22       |

| data arrival time             |           | 11.16      |

| slack (VIOLATED)              |           | -1.93      |

Slack = data required time - data arrival time = (8.33+1.66-0.77)-(3.29+7.87) = -1.93ns

# **Clock Skew Analysis**

The difference in the arrival times of the clock signals between two sequentially-adjacent registers (clock skew) may cause a design to malfunction with short data paths. The most efficient method to eliminate the short data path problem is to minimize the clock skew by using the low-skew global routing resources for clock signals.

Refer to the *Static Timing Analysis Using Designer's Timer* application note for information on clock skew analysis (<a href="http://www.actel.com/documents/Static Timing Analysis.pdf">http://www.actel.com/documents/Static Timing Analysis.pdf</a>).

#### To measure clock skew:

1. Specify clock frequency. In order to obtain hold margin calculations, Timer requires that you specify a clock frequency. Timer uses the frequency to calculate the period, which it needs to evaluate the margin for adjacent flip-flops with alternate clock edges. If you do not enter a clock frequency in the summary tab, you will not get any results.

To enter a frequency, select the desired clock under **Select Clock**, and enter a frequency under **required** in the Summary tab. Click **Set** when you are done.

- 2. Set your **Preferences** in Timer. To measure clock skew, perform hold time analysis for **BEST** case in **Shortest** path mode. Set the **Case** in **File** -> **Preferences**.

- 3. Run Violations Report. A report is available from Timer that provides a summary of timing margins for all paths in the design. From the **Tools menu**, choose **Report Violations**. This report lists the following categories:

- · Section Clock constraints violation

- · Section Max Delay constraints violation

· Section Min Delay constraints violation

To find a summary of hold time margin in your design for the given operating conditions, refer to the timing path listed under Section Min Delay constraints violations.

The first column defines the slack for each path. Positive values represent margin, negative values represent a violation.

4. Perform detailed analysis. To see the details of a given path, go to the **Paths** tab in Timer. You can look for a specific path by creating a new path set for the specific path(s) you are interested in. To create a path set, choose **Add set of paths** from the **Edit** menu. Refer to the <u>Paths tab</u> for information on how to add a set of paths.

Once you have defined the new path set, click the set to display the path list in the lower spreadsheet. Then highlight the path you are interested in, right click and select **Expand Path**.

5. Review **Expanded Path** window. The expand path window shows details of the calculations performed in the clock skew analysis.

The margin is calculated by adding the clock propagation delay of the master register to the data path delay between the two registers. This is the data arrival time. Then the clock propagation to the slave register is subtracted from the sum, giving the final slack value. If alternate clock edges are used for adjacent registers, Timer considers the clock period accordingly.

# **Adding Path Sets**

Create and add path sets to the <u>Paths</u> tab to determine delay information and enter constraints. User-defined sets enable you to customize the sets that are available for analysis. By creating custom sets, you can simplify timing analysis and constraint setting for specific blocks or paths in your design.

For example, if you are concerned about timing of the lower-level block "sub\_block\_1" in your design, you can create a set that only includes timing paths in that block.

#### To add a set:

- 1. Click the **Paths** tab.

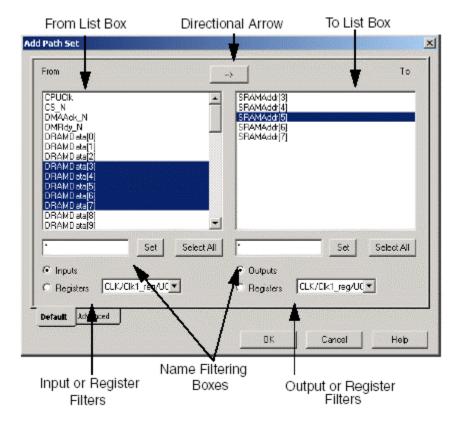

- 2. From the **Edit** menu, choose **Add Set of Paths**. The **Add Path Set** dialog box consists of two screens, **Default** and **Advanced**. The **Advanced** tab enables you to use keywords to create a set. For more information on using keywords.

Add Path Set Dialog Box

- 3. Select the desired clock.

- 4. Click the directional button to select path direction.

- 5. Select the desired Inputs (all input pad pins) or Registers (all input pins on the flip-flops and latches).

Use the drop-down menus to choose the active clock. Choose All Clocks for both to find delays for all register-to-register paths. Select the Outputs radio buttons to filter the **From** and **To** list boxes (it limits the From and To list boxes to all output pad pins).

Select your desired starting and ending points in the **From** and **To** list boxes. Naming filters are provided to limit the list of terminals in the display. The naming filters use the \* character as a wildcard and the / character to delimit levels of hierarchy.

For example, use \* to filter for all terminals; \*:E to filter for all terminals with pin E; U1/\* to filter for all terminals in block U1; and U1/\*:E to filter for all terminals in block U1 with a pin E. You can also use multiple wildcards such as \*/U1/\*:E. After entering your naming filter, click the **Set** or **Select All** button.

### If the directional button is pointing right:

- 1. Select a starting point in the **From** list. The **To** list box displays all corresponding endpoints.

- 2. Select one or more endpoints in the To list box that complete the path set. Click the Select All button to select all endpoints.

#### If the directional button is pointing left:

- 1. Select the endpoint in the **To** list box. The **From** list box displays all corresponding starting points.

- 2. Select one or more starting points in the **From** list box. Click the **Select All** button to select all.

Click **Apply** to add the path set to the **Paths** tab. Continue creating and adding sets. When you are done, click **Close** to close the **Add Path Set** dialog box.

# Add a "one input to all outputs" path set

To show one input to all outputs, you must add the set to the **Paths** tab. You can then view delay details and set constraints.

#### To show one input to all outputs:

- 1. In the Paths tab, select Add Set of Paths from the Edit menu. The Add Path Set dialog box appears.

- 2. Select the **Inputs** and **Outputs** radio buttons.

Make sure the directional arrow is pointing to the right, from **Inputs** to **Outputs**. Click the arrow to change its direction.

- 3. Select the desired input starting point in the **From** list box.

- 4. Click the **Select All** button to select all outputs.

- 5. Click **OK**. The set showing one input to all outputs is added to the **Paths** tab.

# Add an "all inputs to one output" path set

To show all inputs to one output you must configure and add the set to the Paths tab.

#### To create a set showing all inputs to one output:

- 1. In the Paths tab, from the Edit menu, click Add Set of Paths. The Add Path Set dialog box appears.

- Select the Inputs and Outputs radio buttons.

- 3. Click the directional arrow to point it left.

- 4. Choose the desired output endpoint in the **To** list box.

- 5. Select all inputs (all starting points), by Clicking on the **Select All** button under the **From** list box.

- 6. Click **OK**. The set showing all inputs to one output is added to the **Paths** tab.

# Edit or Remove a Path Set

#### To edit a path set:

- 1. Select the set in the **Paths** tab.

- 2. In the Edit menu, click Edit Set of Paths, or right-click and choose Edit Set. This displays the Edit Set dialog box.

- 3. Edit the **Path Set** and click **OK**.

### To remove a path set:

- 1. Select the set in the **Paths** tab.

- 2. In the Edit menu, click Remove Set of Paths, or right-click and choose Remove Set from the shortcut menu. The set is removed.

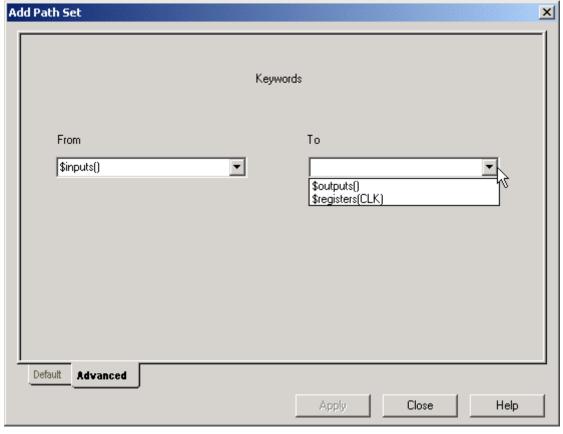

# Adding/Removing sets with keywords

The **Advanced** tab in the **Add Set** dialog box enables you to use keywords (macros that represent various sets of terminals) to create a set. You must **Commit** your changes in the main window to save your constraints.

Add Path Set - Advanced Tab

Keywords for the SX-A, eX, Axcelerator, ProASIC, ProASIC<sup>PLUS</sup>, ProASIC3, and ProASIC3E families are explained in the <u>Keyword Filters</u> section.

#### Supported keywords include:

- \$inputs() All input and bidirectional pins.

- \$outputs() All output and bidirectional pins.

- \$registers(clock\_name) The pins of all registers driven by the clock whose name is clock\_name.

#### To create a set using keywords:

- 1. Click the **Paths** tab.

- 2. In the Edit menu, select Add Set of Paths.

- 3. Click the **Advanced** tab.

- 4. Enter the From keyword or select a keyword from the From drop-down list box to define the From set.

- 5. Enter the **To** keyword or select a keyword from the drop-down list box to define to set.

- 6. Click **OK**. This displays paths for the keyword set in the **Paths** tab.

# **Timing Constraints**

# Specifying timing constraints

Timer enables you to specify timing constraints and requirements for clocks and paths. These constraints are used in timing driven layout and in timing analysis. In order to run timing driven layout, you must import an SDC or invoke timer in pre-layout mode and enter the constraints in timer GUI. Commit the changes before exiting timer.

For ProASIC, ProASICPLUS, and ProASIC3/E, Actel recommends that you use timing constraints set through the SDC import or Timer GUI. For Axcelerator, you can run timing driven place-and-route even if you have not set any user constraints.

The following table shows the correlation between SDC and Timer GUI:

|                     | SDC           | Timer GUI       |

|---------------------|---------------|-----------------|

| create_clock        | with waveform | with duty cycle |

| set_max_delay       | X             | X               |

| set_multicycle_path | X             | N/A             |

| set_false_path      | X             | X               |

| set_load            | X             | N/A             |

| clock exception     | N/A           | X               |

Note: Timer supports set\_false\_path -through only. Although an SDC file allows set\_false\_path with combination of -from, -to and -through arguments, the tool ignores the constraint if it is not a -through only. The -from or -to arguments cannot be set in the Timer GUI. The set\_multicycle\_path constraint cannot be set in the Timer GUI. It can be set only through SDC.

You can set the load on a port using the I/O Attribute Editor.

For details on how to set the timing constraints for ProASIC PLUS family, refer to the application note at:

http://www.actel.com/documents/APATimingClosure.pdf

# **Constraint guidelines**

# **Delay Constraint Guidelines**

Delay constraints control the Timing-Driven Layout engine. You can define these constraints using Timer or by importing an external DCF or SDC file. The timing-driven layout engine considers the defined delays when allocating silicon resources with the goal of meeting or beating all constraints if possible. The timing-driven layout engine evaluates the performance criticality of one function versus another when allocating device resources. Because resources are limited, use the following guidelines to ensure the defined constraints meet the needs of the design without impairing device resources.

### **General Guidelines**

Set Sufficient Constraints - All constraints for the design should be defined to ensure correct operation of the Timing-Driven

Layout engine. Timing-Driven Layout considers networks that have not been defined as "don't care" paths, which have a low

priority for resource allocation. If these undefined paths are actually critical, they may fail to meet performance demands.

- Avoid Unnecessary Constraints Describe "don't care" paths to free high performance device resources. Designer provides false paths, clock exceptions, and global stops for the user to define these "don't care" paths. (See <u>Clock exceptions</u> and set false path).

- Avoid Over-Constraining The Timing-Driven Layout engine is designed to achieve or exceed the delay constraint defined

(less than or equal). Defining a constraint shorter than is actually required for margin can have a negative impact on the

performance of the device because of competition for device resources.

# Specifying clock constraints

Use the Clocks tab to assign values to each clock network in your design.

#### To assign clock constraints:

- 1. Click the Clocks tab.

- 2. Select the clock of interest in the **Select Clock** pull-down menu in the toolbar.

- Specify the timing requirements. In the Constraints area, define the Required and Duty Cycle areas. Select MHz or ns from the dop-down menu.

- 4. Click Set.

# **Clock exceptions**

Timer enables you to specify global clock constraints. If you have paths that are not required to meet the global constraint (for example, multi-cycle paths), then list them as exceptions. The **Clocks Exceptions** area on the **Clocks** tab provides a mechanism for doing this. A terminal specified as a clock exception will cause all paths beginning or ending at this terminal to be unconstrained by the global timing constraint.

#### To add or remove terminals from the Clock Exception List:

- 1. Click the Clocks tab.

- 2. Select the Clock name from the drop-down menu.

- 3. Enter a constraint in the Constraints area and click Set.

- 4. Select **Source** or **Sink** in the **Clock Exceptions** area. The **Clock Exceptions** area displays the Pins. The terminals of the sequential device are displayed using an <instance\_name>:<pin\_name> format.

- For example, a DFM with an instance name of U1\FF1 will have a single source terminal, U1\FF1:CLK, and three sink terminals: U1\FF1:A, U1\FF1:B, and U1\FF1:S.

- 5. Use the **Filter** field to further sort the list of clock pins. Naming filters are provided to limit the list of terminals for consideration. The naming filters use the \* character as a wildcard and the / character to delimit levels of hierarchy.

- For example, use \* to filter for all terminals; \*:E to filter for all terminals with pin E; U1/\* to filter for all terminals in block U1; and U1/\*:E to filter for all terminals in block U1 with a pin E. After entering your naming filter, click the **Set** or **Select All** button. Multiple \* and / characters may be used.

- 6. **Add** or **Remove** the clock exception. To add a clock exception, highlight the desired entry from the **Clock Pins** list and click **Add**. To remove an exception, highlight it in the **Exceptions** list and click **Remove**.

- From the File menu, choose Commit to commit changes.

# Path constraints - specifying or removing

You can specify a timing constraint on a specific path or groups (sets) of paths.

#### To specify a timing constraint for a path set:

- 1. Click the **Summary** or **Paths** tab.

- 2. Select a Path set.

- 3. Enter the timing constraint. On the **Summary** tab enter the constraint in the **Required** text box and click **Set**. On the **Paths** tab enter the constraint in the **Max Delay** column.

#### To specify a timing constraint for a specific path:

- 1. Click the **Paths** tab.

- Click the corresponding set in the Set grid.

- 3. Select the path in the path grid.

- 4. Enter the timing constraint in the **Max Delay** column.

### **Removing Constraints**

You can remove all constraints or just selected constraints. To remove all constraints choose **Remove All Constraints** from the **Edit** menu.

#### To remove select constraints on the Paths tab:

- 1. Click the **Paths** tab.

- 2. Select the path set with the constraint you wish to remove.

- 3. In the Edit menu, choose Remove Selected Constraints.

To remove select constraints on the Summary tab, delete the constraint in the Required text box and click Set.

# **Timing Results**

# **Export Results**

From the Paths tab, you can export the path or set grids in a text file.

#### To save your results to a text file:

- 1. Click the <u>Paths</u> tab.

- 2. In the File menu, choose Export Path Grid or Export Set Grid. This displays the Save As dialog box.

- 3. Choose a destination on your disk, enter a File Name and click Save.

### Commit before you exit

If you wish to save the constraint requirements entered into Timer, you must **Commit** your Timing results before exiting Timer.

Commit before you exit Generate reports

To commit your results choose **Commit** from the **File** menu before exiting, or click **Yes** when asked if you would like to commit your results before exiting. Timer saves your timing constraints to Designer's temporary design database.

# **Generate reports**

The timing report enables you to quickly determine if any timing problems exist in your design. The timing report lists the following information:

- Delay from input I/O to output I/O (longest or shortest, depending on your Preferences).

- Delay from input I/O to internal registers (longest or shortest, depending on your Preferences).

- Delay from internal registers to output I/O (longest or shortest).

- Delays for each clock network (longest or shortest).

- Delays for interaction between clocks networks (longest or shortest).

#### To generate a timing report:

- From the Tools menu, choose Report Paths. The <u>Timing Report</u> dialog appears. The <u>External Setup-Hold Timing</u> check box and the <u>Slack Threshold</u> text box are explained in the <u>Timer Report</u> dialog box section.

- 2. Click **Options** to specify more settings for your report. This displays the **Preferences** dialog box.

- 3. Verify your timing analysis preferences. Timer uses these preferences to generate your report.

- Maximum List Size:

**Longest/Shortest Path(s)** - Defines the number of paths to display in the report (default is 1) **Expanded Path(s) in List** - Defines the number of expanded paths to display in the report (default is 15)

• Sort By:

Actual - Sort paths by actual delays.

Slack - Sort paths by slack delays.

This option is available only if you have entered timing constraints.

- Case: Specifies your operating conditions, Best (0 degrees centigrade), Typical (25 degrees centigrade), and Worst (70 degrees centigrade).

- Break Path at Register The default timing paths break at all clock, gate, clear, and preset pins. Clear the check boxes in Break Path

at Register to generate a timing report that displays paths that pass through (and do not "break") at all Clock, Clear, Gate, and Preset

pins.

Once you are satisfied with your selections, click **OK** in the **Preferences** dialog box and then click **OK** in the **Timing Report** dialog box. The timing report is displayed in a separate window.

# **Violations Report**

For families that use the <u>pin-to-pin timing model</u>, the Violations report enables you to obtain constraint results sorted by slack. You can now view Max Delay violations as well as Min Delay violations in the report.

Keyword Filters Levels of Keywords

# **Keyword Filters**

# **Keywords**

Keywords enable you to filter out any unwanted paths or instances, making it easier to view critical paths in the design and limiting the paths displayed for a particular set. The use of keywords is only supported for pin-to-pin delay families.

Use keywords to create custom sets for Timer's Paths tab screen.

The use of keywords is only supported for pin-to-pin delay families (for an explanation of pin-to-pin and input-to-input delay families, see <u>Delays, PLLs, RAMs, and FIFOs</u>). Use keywords to create custom sets for Timer's **Paths** tab screen. Refer to <u>Adding/Removing</u> sets with keywords for details on how to enter keywords.

Keywords enable you to filter out any unwanted paths or instances, making it easier to view critical paths in the design and limiting the paths displayed for a particular set. Timer uses two types of keywords, first- and second-level.

### **Levels of Keywords**

The first-level keywords enable access to the main objects of the design, such as registers, while the second-level keywords enable access to a sub-list of these main objects. For instance, *\$registers()* is a first-level keyword that enables access to all the registers of the design. This list includes clock pins, data pins, enable pins and, asynchronous pins.

If the *\$registers()* keyword is combined with the second-level keyword *\$datapins()*, the related command is applied only to the data pins of the registers. You can use a second-level keyword only with a first-level; second-level keywords may not be used alone. In Timer, only the first-level keyword *\$registers()* may be combined with the second-level keywords. Use the colon ":" without any spaces to combine first- and second level keywords. Keywords and filters are case insensitive.

### **Filtering**

Filter keywords with brackets []. The filter is a string that is used as an identifier (it may contain wild cards). [] with an empty string is not accepted in the macro language. The user can enter \$registers(), \$registers()[filterString], but not \$registers()[].

#### **Functions**

Sometimes you may want to locate objects of the design by defining or identifying other objects. For instance, you might want to analyze delays of all the registers driven by a specific primary clock. Functions can help you locate the registers (objects) by defining the primary clock (identifier).

To use functions, the identifier of the object has to be reported between parentheses ( ). This identifier may contain wild cards and can also be another keyword. For example:

# **Supported Keywords**

Timer supports the keywords listed below.

| First-Level Keywords                                               | Second-Level Keywords                                                                         |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| <pre>\$registers() \$inputs() \$outputs() \$clocks() \$ports</pre> | <pre>\$datapins() \$clockpins() \$asyncpins() \$enablepins() \$outputpins() \$inputpins</pre> |

|                                                                    | \$allpins                                                                                     |

#### **First-Level Keywords**

Each keyword has two identifiers, a long version and a short version. They both have exactly the same function. The first-level keywords are defined below.

\$registers(ClockName) or \$reg(ClockName)

The keyword above only displays the registers (edge-triggered flip-flops and level-sensitive latches) controlled by the clock *ClockName*. If no *ClockName* is specified, this keyword will cause all the registers of the design to be displayed.

\$inputs() or \$in()

This keyword only displays all the primary inputs of the design.

\$outputs() or \$out()

This keyword only displays all the primary outputs of the design.

"\$Clocks()" or "\$CK()" only displays the primary clocks of the design.

\$ports(InstanceName) or \$po(InstanceName)

This macro replaces all the primary inputs and outputs of the design.

## **Second-Level Keywords**

While first-level keywords allow access to the main objects of the design, such as registers, second-level keywords give access to a sub-list of these main objects.

Currently, second-level keywords can only be used with the first-level keyword *\$registers()*. A first-level keyword is separated from a second-level keyword with the colon ":" character, without any spaces.

As with first-level keywords, most second-level keyword have two identifiers, a long version and a short version. Each has the exact same function. In the following examples, it is assumed that the notion of event and pin are implicit.

"\$DataPins()" or "\$dp ()" indicates all the data pins of a register. For example:

| \$registers(CLK):\$dp() | Displays the data pins of all the registers controlled by CLK |

|-------------------------|---------------------------------------------------------------|

|-------------------------|---------------------------------------------------------------|

<sup>&</sup>quot;\$OutputPins()" or "\$qp()" indicates all the output pins of a register. For example:.

Keywords Second-Level Exceptions

| \$registers(CLK):\$qp() | Displays the output pins of all the registers controlled by the primary clock CLK |

|-------------------------|-----------------------------------------------------------------------------------|

|-------------------------|-----------------------------------------------------------------------------------|

"\$ClockPins()" or "\$cp()" indicates all the clock pins of a register. For example:.

| \$registers(CLK):\$clockpins() | Displays the clock pins of all the registers controlled by the primary clock CLK. |

|--------------------------------|-----------------------------------------------------------------------------------|

|--------------------------------|-----------------------------------------------------------------------------------|

<sup>&</sup>quot;\$AsyncPins()" or "\$ap()" indicates all the asynchronous pins of a register (preset and clear).

<sup>&</sup>quot;\$EnablePins()" or "\$ep()" indicates all the enable pins of a register. For example:

| <pre>\$registers(CLK):\$ep()</pre> | Displays the enable pins of all the registers controlled by the primary clock CLK. |

|------------------------------------|------------------------------------------------------------------------------------|

|------------------------------------|------------------------------------------------------------------------------------|

\$inputpins() or \$ip() indicates all the input pins of a register. For example:.

| <pre>\$reg(CLK):\$inputpins()</pre> | Displays the input pins of all the registers controlled by the CLK |

|-------------------------------------|--------------------------------------------------------------------|

|-------------------------------------|--------------------------------------------------------------------|

\$allpins() indicates all the pins of a register. For example:.

| <pre>\$registers(CLK):\$all- pins()</pre> | Displays the pins of all the registers controlled by the CLK |

|-------------------------------------------|--------------------------------------------------------------|

|                                           |                                                              |

## **Second-Level Exceptions**

In order to provide more flexibility, the second level keywords can be coupled with exceptions. For instance, if you want to select all the input pins of the registers except the clock pins, you can use the following macro:

\$registers(clk):\$inputpins(TmacEx\_CLOCKPINS)

The available exceptions are listed in the following table:

| Exception        | Result                                                                              |

|------------------|-------------------------------------------------------------------------------------|

| TmacEX_CLOCKPINS | The clock pins will not be returned from the pins indicated by the 2nd level macro. |

PLLs Calculating Delays

| TmacEX_DATAPINS   | The data pins will not be returned from the pins indicated by the 2nd level macro.         |

|-------------------|--------------------------------------------------------------------------------------------|

| TmacEX_ASYNCPINS  | The asynchronous pins will not be returned from the pins indicated by the 2nd level macro. |

| TmacEX_INPUTPINS  | The input pins will not be returned from the pins indicated by the 2nd level macro.        |

| TmacEX_ENABLEPINS | The enable pins will not be returned from the pins indicated by the 2nd level macro.       |

| TmacEX_OUTPUTPINS | The output pins will not be returned from the pins indicated by the 2nd level macro.       |

## **Calculating Delays**

## Delays, PLLs, RAMs, and FIFOs

Actel Timer uses two different timing models, pin-to-pin and input-to-input. The first type uses a pin-to-pin timing model, because Timer reports a pin-to-pin delay. The second type uses an "input-to-input" timing model, because Timer reports the delays from an input gate to the input of the next gate by lumping the gate and net delays together.

ACT1, ACT2, ACT3, DX, MX, and SX devices use the input-to-input timing model, while the SX-A, RTSX-S, eX, Axcelerator, ProASIC, ProASIC<sup>PLUS</sup>, and ProASIC3/E families use the pin-to-pin timing model. Some timing analysis features are specific to the different timing models; exceptions are noted in the help.

The delay for pin-to-pin devices is reported until the input pins of the registers. Therefore, setup time is not included in the delay. However, the register setup and hold, as well as the clock skew, are taken into account during the analysis of setup check and hold check when identifying timing violations. Setup, hold, and clock skew are also taken into account during clock frequency estimation.

For information on the setup and hold process in Timer, see the <u>Expanded Paths window</u>. It enables you to view clock network insertion delay and clock skew information.

#### **PLLs**

The timing tool sees a PLL as a register and a clock generator. Any clock output port in a PLL is a potential clock (and appears in the list of potential clocks for the design). Like all other potential clocks, you can constrain these PLL output clocks by setting any clock constraint independently. The input clock of the PLL on which you set the constraint is not the clock input port of the PLL but the clock driving this clock input port. The driving clock will be a Primary port of the design, a register's output, or another PLL's output.

#### **PLLs for Axcelerator**

By default, when you set a clock constraint on the clock source connected to the clock input of the PLL, Timer automatically computes the clock constraints on the outputs of the PLL (according to the PLLs configuration). Thus, the value of the clock output is equivalent to the clock input multiplied, divided, or shifted by the value of your static configuration.

If you specify a clock constraint for the output clock(s), the PLL ignores the static configuration value and delivers a clock frequency according to your constraints. Timer reports this value accurately. In addition, if you remove your constraints on the output clock(s), the Timer tool recalculates your output frequency according to your static configuration value. For more information on generating PLLs and their logic characteristics, please refer to the *ACTgen Macros Reference Guide* in the online help or in .pdf format.

**Note:** For ProASICPLUS and ProASIC3/E families, the PLL is considered as a register only; there is no output clock computation. Apply constraints on the output of the PLL.

#### **RAMs and FIFOs**

The Timer tool displays blocks of RAM and FIFO as a single "black box," (you have as many black boxes as you have instantiations of RAMs and FIFOs in your design). Thus, if you construct a RAM or FIFO cell out of several RAM blocks, Timer sees and treats the cell as a single black box. Timer does not display timing information within individual black boxes, because all the delays are reported using the interface of the RAM. Timer displays timing information between black boxes and other logic in the design.

Timer treats RAMs and FIFOs as registers, and like any register, they have clock signals. For more information about RAMs and FIFOs, please refer to the *ACTgen Macros Reference Guide*, in the online help or in .pdf format.

FIFO: Timer displays the paths to the FIFO flags depending on their clock. Timer shows paths to Empty and Almost Empty with respect to the Read clock; paths to Full and Almost Full are displayed with respect to the Write clock. Check the datasheet for your device to determine whether the FIFO flags change with the Rising or Falling edge of the clock.

## Using ChipPlanner/ChipEditor with Timer

Use ChipPlanner or ChipEditor and Timer together to view place-and-route of Timer paths.

Timer and ChipPlanner

#### To view critical paths:

**RAMs and FIFOs**

- Open Timer and ChipEditor/ChipPlanner from Designer (ChipEditor opens if you are using an ACT1, ACT2, ACT3, DX, MX, SX, SX-A, or eX device; all other devices use ChipPlanner).

- 2. In Timer, click the Paths tab.

- Select a **Path** set in the path set grid. Paths within that set are displayed in the path grid.

- Select the path you wish to expand.

- 5. Expand the path by double-clicking on the path, or in the Edit menu, click Expand Path. The Expanded Paths window opens and displays a single path in the Expanded Paths Grid and a graphical representation of the path in the Chart Window.

- Select a module or net in the **Expanded Paths** dialog box. The module or net is shown in **ChipEditor** or **ChipPlanner**.

Refer to the online help for more information on how to use the ChipEditor/ChipPlanner tools.

You can add and remove break points in Timer while you use the ChipEditor/ChipPlanner tool.

## Timing delay constraint definitions

The following terminology appears in the <u>description</u> of constraints for Timer.

#### **DTL Terminals**

Timing Driven Layout terminals define the starting (or source) and ending (or sink) points for a signal path. They are always I/Os or sequential elements; no intermediate combinatorial element is currently supported as a terminal.

### **Signal Path**

The signal path describes a consecutive sequence of logic and nets, the first net being driven by a start terminal, and the last net driving a macro input pin of the end terminal.

#### **Network**

A network can consist of 1 or more start terminals and 1 or more end terminals. All signal paths connecting any start terminal to any end terminal are included in the network. Only one delay value can be assigned to each defined network. Networks can be defined implicitly by a common clock (synchronous network) or explicitly by a defined set of terminals. Network and Paths are used interchangeably.

### **Path Delay**

The path delay defines the sum of all the individual delays of the nets and the logic macros in the signal path.

### **Delay Constraint**

A delay constraint defines a fixed amount of time required for a signal to propagate from all starting terminals to all ending terminals for a network.

#### **Don't Care Path**

A signal path in which the delay is considered to be infinite.

### **Global Stop**

A defined intermediate point in a network that forces all paths through the defined point to be don't care paths regardless of any constraint assignment.

## **Clock Exception**

A terminal in a synchronous network that should be excluded from the specified clock period. The exception can remain undefined (don't care) or can be assigned a unique value in the Path Constraint Editor.

## **Timer Glossary of Terms**

This glossary defines terms and concepts used in the Timer online help.

#### clock exception

A terminal in a synchronous network that should be excluded from the specified clock period. The exception can remain undefined (don't care) or can be assigned a unique value in the Path Constraint Editor.

#### critical path

The path within a design that dictates the fastest time at which an entire design can run. This path runs from the source to a sink node such that if any activity on the path is delayed by an amount t, then the entire circuit function is delayed by time t.

#### delay constraint

A delay constraint defines a fixed amount of time required for a signal to propagate from all starting terminals to all ending terminals for a network

#### destination

An ending point, sink node, for a timing analysis path, often the data input of a synchronous element or pad.

#### don't care path

A signal path in which the delay is considered to be infinite.

### **Dynamic Timing Analysis**