# Actel® Silicon Explorer II

User's Guide

#### Actel Corporation, Sunnyvale, CA 94086

© 2004 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 5029134-0

Release: March 2004

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel. Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document. This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

Trademarks

Actel and the Actel logotype are registered trademarks of Actel Corporation.

Microsoft, Windows, Windows NT, and Windows 2000 are trademarks or registered trademarks of Microsoft Corporation.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

#### Table of Contents

|   | Introduction                    |

|---|---------------------------------|

|   | New Software Support            |

|   | System Requirements             |

|   | Connecting to the PC            |

|   | Software Settings               |

|   | 8                               |

| 1 | Connecting Silicon Explorer II  |

|   | Powering Silicon Explorer II    |

|   | Connector Types                 |

|   | Connecting Silicon Explorer II  |

|   | 8                               |

| 2 | Silicon Explorer Software       |

|   | Using the Command Module        |

|   | Using the Analyze Module        |

|   |                                 |

| A | Debugging AX/eX/SX/SX-A Devices |

|   | Using Silicon Explorer II 25    |

|   | Probe Circuit Control Pins      |

|   | Diagnostic Pin Consideration    |

|   |                                 |

| В | Location of the SDO Pins        |

|   |                                 |

| C | Troubleshooting                 |

|   | Errors and Troubleshooting      |

|   | General Information             |

|   | Software Setup                  |

|   | Hardware Setup                  |

|   | -                               |

|   | Index                           |

**Table of Contents**

## Introduction

This user's guide describes procedures for connecting and using Silicon Explorer II (SE II), debugging, and analyzing devices. For a more detailed description, refer to the online help system included with the software (select the Help command from the Help menu).

Silicon Explorer II enables control of the ActionProbe circuitry, a patented architectural feature built into all of Actel's antifuse devices that allows access to any internal node from selected external pins. SE II integrates two diagnostic tools, the Command module and the Analyze module, into a single diagnostic and logic analysis device that attaches to a PC's standard COM port.

The Command module of the Explore software lists all the observable nets in the FPGA. Select the desired net in the list and click the PRA or PRB button to display the signal on the Analyze module. The Command module also reads back the design's checksum. Also, it is possible to read back the CHECKSUM of a device after it has been secured. You can use the design's checksum to verify that you programmed the correct design in the FPGA.

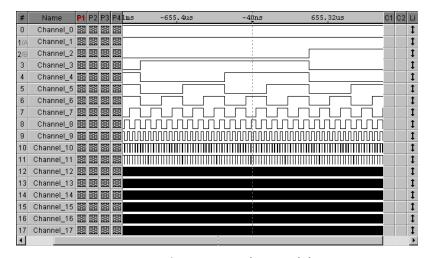

The Analyze module is an 18-channel logic analyzer that automatically displays the signals for both probe outputs (and up to 16 additional signals) on the target system. You may sample data asynchronously at 66 MHz. Channel 1 and 2 of the logic analyzer connect to the PRA and PRB signals on the FGPA automatically. Silicon Explorer II uses the remaining 16 channels of the logic analyzer to examine other signals on the board.

# **New Software Support**

Silicon Explorer version 5.0 SP2 software offers support for the following devices:

- AX2000

- RTAX1000S

- RTAX2000S

## **System Requirements**

The system requirements for Silicon Explorer II are:

- Designer R1-2000 or later

- · Pentium-133 or equivalent

- Microsoft® Windows 98 or NT<sub>TM</sub> 4.0 SP6, XP, 2000

- 8 MB RAM (minimum); 16 MB recommended

Connecting to the PC

## Connecting to the PC

Silicon Explorer II connects to a standard serial port using an 8250 or 16550 UART. Establish communication via the 9-Pin D-Sub connector.

# **Software Settings**

Silicon Explorer II sets itself to Demo mode on installation. From the Device menu, select Silicon Explorer II or Silicon Explorer, depending on your version of the hardware. Choose the desired port (COM1 through COM4) from the Port drop-down list in the Device menu. The software continuously polls the hardware for activity. Setting the port to the Demo mode prevents the application from opening any COM ports on your system. The serial port saves information in the "analyze.ini" file found in your Windows directory. The default data transfer speed is 115,200 baud. At this speed data transfer for the entire buffer is less than 15 seconds.

You can download the latest version of the Explorer software from the Actel website at http://www.actel.com/support/updates or at http://www.actel.com/custsup/updates/siliexp/index.html

Note: Many notebook computers share the external COM port with a built-in infrared (IR) port. You may have to enter your CMOS setup menu to enable the external COM port.

# **Connecting Silicon Explorer II**

This section describes the procedures required to connect Silicon Explorer II to your device, powering Silicon Explorer II, SE II connector types, logic analysis, and the Explore software.

# Powering Silicon Explorer II

SE II draws power from the external power supply (provided) or by connecting the  $V_{\rm IO}$  pin to a power source (such as might exist on a PCB). You must connect  $V_{\rm IO}$  to a reference voltage when using the external power supply. Actel recommends using the external power supply when the target system cannot supply enough current to run SE II. See Table 1-1 for a list of possible power configurations.

I/O Power Supply

External SE II Power Supply

VIO

2.5V

Required

2.5V

3.3V

Optional<sup>1</sup>

3.3V

5.0V

Optional<sup>a</sup>

5.0v

Table 1-1. Power Configurations for Silicon Explorer II

When you apply power, the yellow "heart beat" LED on Silicon Explorer II begins to blink.

Actel designed Silicon Explorer II hardware to withstand abuse normally found in a lab environment. However, long term exposure to out-of-range conditions can cause failure. In particular, long term connection to reverse- or over-voltage power conditions can cause thermal failure.

## **Current Consumption**

Silicon Explorer II is a CMOS device and exhibits very low current consumption when idle. Current consumption rises rapidly to several hundred milliamps during acquisition. If your power supply is unable to supply the necessary current, SE II or your target may reset.

<sup>1.</sup> If your current system is limited, you must use the external power supply and use VIO as the reference voltage. See Table 1-2 for more information about SE II current requirements.

Connector Types Logic Analysis

Table 1-2 is a guide to typical current consumption based on an acquisition rate at 5V — current will be proportionately higher at 3V.

| Acquisition Rate | Current@5V |

|------------------|------------|

| IDLE             | 75ma       |

| 10 MHz           | 300ma      |

| 20 MHz           | 400ma      |

| 50 MHz           | 500ma      |

| 100 MHz          | 700ma      |

Table 1-2. Typical Current Consumption

# **Connector Types**

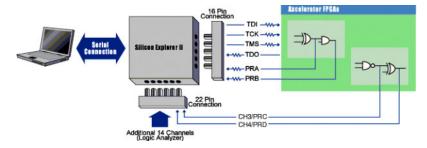

Silicon Explorer II has a 22-pin (18 channels, a clock, VIO, GND, and clock GND), a 26-pin, and a 16-pin connector for controlling the ActionProbe circuitry and reading the design checksum. Table 1-3 is a summary of the connector pins and their functions.

| Connector Type | Mode                |

|----------------|---------------------|

| 22-pin         | Logic Analysis      |

| 16-pin         | ActionProbe Control |

| 26-pin         | Not Used            |

Table 1-3. Connector Types

## **Logic Analysis**

Actel Silicon Explorer II ships with a replaceable target cable assembly (TCA-8020A) that interfaces Silicon Explorer II with your target system. To connect Silicon Explorer II, align the short red wire on the TCA-8020 with no dot on the case and fully insert the 2mm header. The contacts on the TCA-8020 accept standard 0.025" round or square test accessories.

Connect any of Silicon Explorer IIs 18-channel leads to the desired target signals using standard test accessories.

The Silicon Explorer units come with cables that are terminated with a connector so you can insert a post on the board. Also we include a bag of clips that attach to these connectors to clip onto a post or pin of the device, or another cable.

#### **Probe Leads**

Connect the probe leads by attaching one of two supplied cable assemblies.

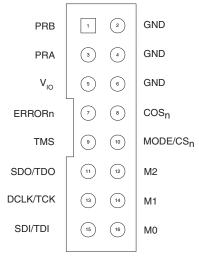

One 16-pin cable assembly terminates in individual 0.025 connectors that connect to 0.025 headers or microclips according to the labels on the wires. The other assembly interfaces directly to the target board with a 16-pin header when you install the target according to the pin-out shown in Figure 1-1.

Figure 1-1. Silicon Explorer II Probe Connector Pin-Out

Connect the probe leads according to Table 1-4 below.

Table 1-4. Matching Probe Pins to Device Pins <sup>1</sup>

| Probe            | Act1, 40MX | ACT2, 42MX,<br>3200DX | SX/SX-A/eX |

|------------------|------------|-----------------------|------------|

| Mode             | Mode       | Mode                  | Not Used   |

| GND <sup>2</sup> | GND        | GND                   | GND        |

| Probe           | Act1, 40MX       | ACT2, 42MX,<br>3200DX | SX/SX-A/eX       |

|-----------------|------------------|-----------------------|------------------|

| SDI/TDI         | SDI              | SDI                   | TDI              |

| DCLK/TCK        | DCLK             | DCLK                  | ТСК              |

| SDO/TDO         | PRA              | SDO                   | TDO              |

| TMS             | Not Used         | Not Used              | TMS              |

| V <sub>IO</sub> | V <sub>CCI</sub> | V <sub>CCI</sub>      | V <sub>CCI</sub> |

| PRA             | PRA              | PRA                   | PRA              |

| PRB             | PRB              | PRB                   | PRB              |

| Ch3             | -                | -                     | PRC              |

| СН4             | -                | -                     | PRD              |

Table 1-4. Matching Probe Pins to Device Pins (Continued)<sup>1</sup>

2. You may connect any or all GND pins. For best results, connect all GND pins.

Note: Chan 16/QO, Chan 17/Q2, and Chan 0/CH0/TRIG refers to a feature in a previous product and is not available in Silicon Explorer.

# **Connecting Silicon Explorer II**

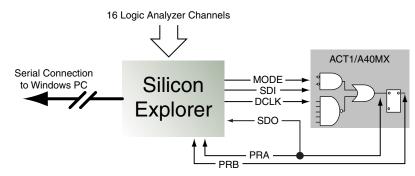

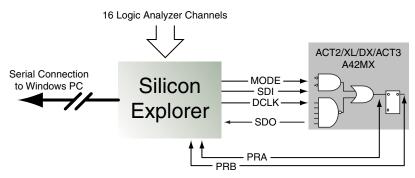

The diagrams below describe, in detail, how to connect the Silicon Explorer II for the various device families. Figure 1-2 shows how to connect Silicon Explorer II to the ACT1/A40MX devices and

<sup>1.</sup> ERRORn, CONn, M2, M1, M0 pins are not required for use with Silicon Explorer II.

Fig. 1-3 shows the setup for ACT2/XL/ACT3/DX and A42MX devices, and Figure 1-4 shows the correct setup for SX/SX-A and eX devices.

# ACT1/A40MX Silicon Explorer Setup

Figure 1-2. ACT1/A40MX Silicon Explorer II Setup

# ACT2/XL/ACT3/DX/A42MX Silicon Explorer Setup

Figure 1-3. ACT2/XL/ACT3/DX/A42MX Silicon Explorer II Setup

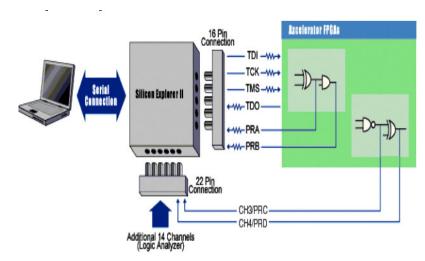

Figure 1-4. SX/SX-A/eX Silicon Explorer II Setup

The probing of an SX-A or eX device may require special setup because it Actel recommends that you use a series 70 ohm termination on all the probe connectors (TDI, TDO, TCK, TMS, PRA, PRB). The 70 ohm series termination is used to prevent data transmission corruption during probing and reading checksum. Figure 1-5 shows the Axcelerator Silicon Explorer II setup.

Figure 1-5. Axcelerator Silicon Explorer II Setup

Probe Leads

Connecting Silicon Explorer II

Connecting Silicon Explorer II

Probe Leads

# **Silicon Explorer Software**

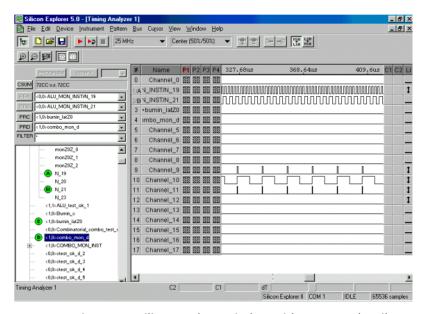

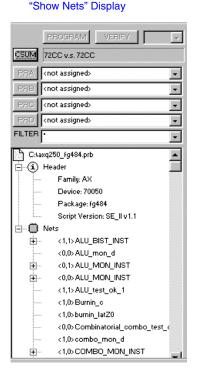

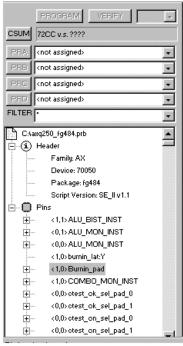

The Explorer software consists of two components, the Command module and the Analyze module. The Command module of the Explore software lists all the observable nets in the FPGA. Use the Command module to verify that you programmed the correct design in the FPGA. The Analyze module is an 18-channel logic analyzer that automatically displays the signals for both probe outputs (and up to 16 additional signals) on the target system. PRC and PRD are not displayed for other device families. Figure 2-1 shows the Silicon Explorer with an Axcelerator probe file loaded.

Figure 2-1. Silicon Explore Window with an AX Probe File

# **Using the Command Module**

The Command module is the interface used to select internal nodes in the Actel FPGA family. The following sections describe exploring with the probe.

Figure 2-2. Command Module

### **Explore the FPGA**

The following procedures describe how to use the Command module to examine an Actel FPGA.

#### To open a probe file:

- Launch Silicon Explorer. Select Silicon Explorer from the Designer menu under Programs in the Start menu.

- 2. Select a Probe (.prb) file to open. Select the Open command from the File menu. Choose (\*.prb) as the File type and double-click the desired probe file. You may also open a probe file in Silicon Explorer by double-clicking the "Open Actel Probe File" icon.

Explore uses a .prb file exported from Designer during analysis. The exported file contains device information, net names, and node location information. After the .prb file opens, verify the information displayed in the tree structure in the Analyze window.

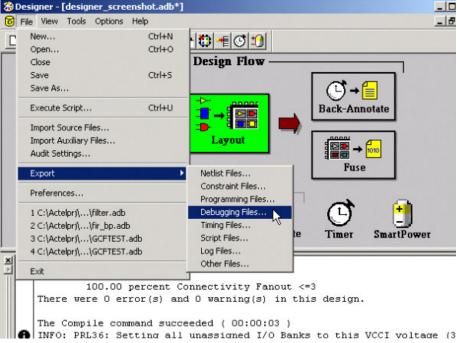

#### To export a probe file from Designer:

- 1. Launch Designer.

- 2. Open your design file.

- 3. Open the Export dialog box. Select Export from the File menu to view the Export dialog box (Figure 2-3).

Figure 2-3. Opening the Export Debugging Dialog Box

- 4. Select Auxiliary File from the File Type pull-down menu.

- 5. Select Probe from the Type pull-down menu.

- 6. Select OK to continue.

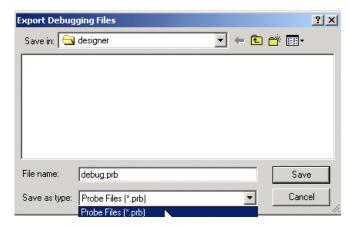

Save the Probe file as a .prd. See Figure 1-4.

Figure 2-4. Saving Probe File as .prd

You can also generate a AFM or probe file using the Generate Programming Files: Fuse Files dialog box. From Figure 1-5, note that the Generate Probe File Also box is checked.

Figure 2-5. Generate Programming Files Dialog Box

#### To verify the checksum:

First, ensure that the SDO/TDO is connected. Then click the Checksum button. Once you open a Probe file and make a device connection, read the checksum of the target device and compare it to the checksum in the Probe file by double-clicking the Checksum button. Table 2-1 lists and explains the error messages.

Checksum: 383A vs. ????

Checksum is not readable because the probe is disconnected or not powered.

The checksum does not match the file.

or

The SDO/TDO probe-side pin is not properly connected to the device. Please see Table 1-4 on page 9 for the proper connection.

Table 2-1. Checksum Error Messages

## To probe a node:

- Select the desired signal from the tree by clicking the net name (see Figure 2-1). You can

use the filter box to search nets quickly. Use multiple wildcard characters ("\*") to restrict

your search.

- Click the PRA or PRB button. Silicon Explorer II routes the selected node to the probe pin and switches the corresponding analyzer input to the probe connector. The Analyze module displays the net name.

You can modify the tree information to reflect the design's internal net names or pin names by rightclicking the Nets icon and selecting either "Show Nets" or "Show Pins". See Figure 2-6 for examples of the two types of displays.

Figure 2-6. Command Module Display Styles

If you cannot find a net, it is possible that the net was optimized by Designer. Refer to "Troubleshooting" for more information about the limitations in probing Actel devices using Silicon Explorer.

# Using the Analyze Module

Follow the instructions below to use the Analyze Module.

#### To use the Analyze Module:

1. Open Silicon Explorer II and check the status in the lower right corner of the display. If you have properly selected the COM port and powered up Silicon Explorer II, then the status is IDLE. The Analyze module captures 64K samples of each channel and uploads them to the host over the serial port. (Figure 2-6).

Figure 2-7. Analyze Module

2. Set acquisition parameters from the tool bar or the pull-down menus. See Table 2-2 for a summary of the parameters.

Table 2-2. Acquisition Parameters

| Acquisition Speed | 10 Khz to 100 MHz asynchronous                                                                                                                                           |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trigger Position  | 25%<br>50%<br>75%                                                                                                                                                        |

| Trigger Pattern   | Click on individual signals in the Pxcolumn to specify don't care, low, high, rising, falling or either edge. The trigger pattern is the logical AND of the 18 patterns. |

3. Once you set the acquisition parameters, click the Run button (red triangle) to begin acquisition. The analyzer begins capturing data until Silicon Explorer II recognizes the trigger pattern or you press the stop button (black square). During the capture period, the status window displays "PRE" for the pretrigger state (although you may not see it if the trigger pattern matches quickly).

Next, Silicon Explorer II enters the "POST" state and samples data after the trigger pattern (or stop button) until it fulfills the posttrigger requirement. Then, it uploads the data to the host (READ State with progress indicator). The entire upload process takes less than 15 seconds, although you may zoom in and view data immediately because the buffer uploads as a background task.

#### **View Data**

Panning and zooming are available in the scroll bars, tool bar, or keyboard control. In addition, dragging a box in the display area zooms the window. Table 2-3 lists keyboard equivalents.

Key Function Zoom In 2X Up Arrow Down Arrow Zoom Out 2X Left Arrow Scroll Earlier (Data moves Right) Scroll Later (Data moves Left) Right Arrow Page Up Jump One Screen Earlier Page Down Jump One Screen Later Home Jump to Trigger

Table 2-3. Keyboard Equivalents

Place cursors by clicking in the display area. Silicon Explorer II displays the time below the channel labels and data values in the C1 and C2 columns. The L or "Live" Column indicates the current state of the 18 channels when the analyzer is in "IDLE."

The Timing Instrument offers many convenient features for viewing, saving, and printing data. More detailed information is available from the online help system (select the Help command from the Help menu).

Explore the FPGA

Using the Analyze Module

Using the Analyze Module

Explore the FPGA

# Debugging AX/eX/SX/SX-A Devices Using Silicon Explorer II

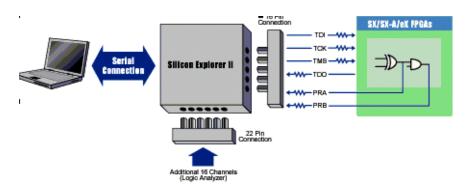

AX, eX, SX, and SX-A devices may require additional attention when debugging. You must control probing on AX, eX, SX and SX-A devices through the IEEE 1149.1 pins. You may configure the IEEE 1149.1 pins as dedicated (JTAG only) or flexible (JTAG or I/O). This section assists you with these and other considerations when debugging SX, SX-A, or eX devices.

## **Probe Circuit Control Pins**

The Silicon Explorer II tool uses the IEEE 1149.1 pins (TDI, TCK, TMS and TDO) to select the desired nets for debugging. The user assigns the selected internal nets to the PRA/PRB pins for observation. Figure A-1 illustrates the connection between Silicon Explorer II and the SX/SX-A/eX FPGA required to perform in-circuit debugging.

Figure A-1. eX,/SX/SX-A Setup

Figure A-2 shows the AX Silicon Explorer setup.

Figure A-2. Axcelerator Silicon Explorer Setup

## **Diagnostic Pin Consideration**

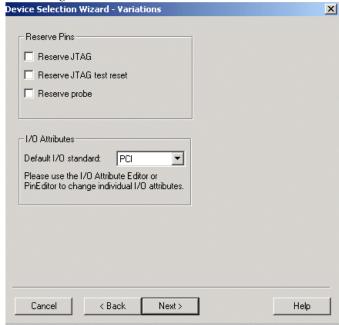

To place the IEEE 1149.1 (JTAG) and probe pins (TDI, TCK, TMS, TDO, PRA and PRB) in the desired mode, select the appropriate check boxes in the "Device Variations" dialog window (as shown in Figure A-3). This dialog window is accessible through the Design Setup Wizard under the Option menu in Designer.

Figure A-3. Diagnostic Pins Configuration

#### To Access the Device Variations Dialog Box in Designer:

- 1. Launch Designer.

- 2. Open your Design.

- 3. Select Device Setup under the Options Menu. The Device Selections dialog box appears.

- Click Next. The Device Variations Dialog Box appears.

#### Dedicat ed JTAG Mode

When you select the "Reserve JTAG Pin" box, you place the FPGA in **Dedicated JTAG mode**, which configures TDI, TCK, and TDO pins for JTAG boundary scan or in-circuit debug with Silicon Explorer II. Also, you enable an internal pull-up resistor on both the TMS and TDI pins

(Figure A-4). In addition, by checking the "Reserve JTAG Pin" box, TDI, TCK and TDO are not available for pin assignment in the Pin Editor.

Figure A-4. Dedicated JTAG Mode

You do not need to specify an internal pull-up resistor; SE II automatically configures TMS and TDI with internal pull-up resistors.

#### Flexible JTAG Mode

When you do not select the "Reserve JTAG Pin" box, you place the FPGA in Flexible JTAG mode, where TDI, TCK and TDO pins may function as user I/Os or JTAG pins. When you select Flexible JTAG mode, you disable the internal pull-up resistors on the TMS and TDI pins. Note that you require an external 10K Ohm pull-up resistor on the TMS pin in this mode (Figure A-5).

Silicon Explorer II transforms TDI, TCK and TDO pins from user I/Os into JTAG diagnostic pins when a rising edge at TCK is detected while TMS is at logical low. The JTAG pins revert to user I/Os when the JTAG state machine is in the Test-Logic reset state.

Figure A-5. Flexible JTAG Mode. Note 10K Ohm Pull-up Resistor

Table 1 enumerates all the possible configuration of the diagnostic pins.

Table 1. Diagnostic Pin Configuration

| Dedicated JTAG Mode                              | Flexible JTAG Mode                                                                  |

|--------------------------------------------------|-------------------------------------------------------------------------------------|

| TCK, TDI, and TDO are dedicated diagnostic pins. | Use TCK, TDI and TDO as I/Os.     You need the 10K pull-up resistor on the TMS Pin. |

# Probe Pins

When you select the "Reserve Probe Pin" box, you direct the layout tool to reserve the PRA and PRB pins as diagnostic pins. This option is merely a guideline. If the Layout tool requires that the PRA and PRB pins be user I/O's to achieve successful layout, then the tool will use these pins as user I/Os. If you assign user I/Os to the PRA and PRB pins and select the "Reserve Probe Pin" option, the Layout tool will override the "Reserve Probe Pin" option.

#### Design Conside rations

Avoid using the TDI, TCK, TDO, PRA, and PRB pins as input or bidirectional ports. Since these pins are active during probing, critical input signals through these pins are not available. In addition, do not program the Security Fuse. Programming the Security Fuse disables the Probe Circuit. However, you can still read the checksum.

# **Location of the SDO Pins**

Tables B-1 through B-3 show SDO pin numbers for ACT2 and 1200XL families.

Table B-1. A1225A/A1225XL

| Package | SDO Pin Number |

|---------|----------------|

| PLCC84  | 52             |

| CPGA100 | Ј9             |

| PQFP100 | 52             |

| VQFP100 | 50             |

Table B-2. A1240A/A1240XL

| Package | SDO Pin Number |

|---------|----------------|

| PLCC84  | 52             |

| PQFP100 | 52             |

| CPGA132 | N12            |

| PQFP144 | 71             |

| TQFP176 | 87             |

Table B-3. A1280A/A1280XL

| Package | SDO Pin Number |

|---------|----------------|

| PLCC84  | 52             |

| PQFP160 | 82             |

| CQFP172 | 85             |

| CPGA176 | P13            |

| TQFP176 | 87             |

| PQFP208 | 103            |

29

Tables B-4 through B-8 show SDO pin numbers for the ACT3 family.

Table B-4. A1415

| Package | SDO Pin Number |

|---------|----------------|

| PLCC84  | 52             |

| CPGA100 | L9             |

| PQFP100 | 77             |

| VQFP100 | 49             |

Table B-5. A1425

| Package | SDO Pin Number |

|---------|----------------|

| PLCC84  | 52             |

| PQFP100 | 77             |

| VQFP100 | 49             |

| CQFP132 | 63             |

| CPGA133 | M11            |

| PQFP160 | 79             |

Table B-6. A1440

| Package | SDO Pin Number |

|---------|----------------|

| PLCC84  | 52             |

| VQFP100 | 49             |

| PQFP160 | 79             |

| CPGA175 | N12            |

| TQFP176 | 87             |

Table B-7. A1460

| Package | SDO Pin Number |

|---------|----------------|

| PQFP160 | 79             |

| TQFP176 | 87             |

| CQFP196 | 99             |

| CPGA207 | P15            |

| PQFP208 | 103            |

| BGA225  | N13            |

Table B-8. A14100

| Package | SDO Pin Number |

|---------|----------------|

| RQFP208 | 103            |

| CQFP256 | 126            |

| CPGA257 | R17            |

| BGA313  | AE23           |

Tables B-9 through B-13 show the SDO pin numbers for A3200DX family.

*Table B-9. A3265DX*

| Package | SDO Pin Number |

|---------|----------------|

| PLCC84  | 52             |

| PQFP100 | 52             |

| PQFP160 | 82             |

| TQFP176 | 87             |

Table B-10. A32100DX

| Package | SDO Pin Number |

|---------|----------------|

| CQFP84  | 42             |

| PLCC84  | 52             |

| PQFP160 | 82             |

| TQFP176 | 87             |

| PQFP208 | 103            |

*Table B-11. A32140DX*

| Package | SDO Pin Number |

|---------|----------------|

| PLCC84  | 52             |

| PQFP160 | 82             |

| TQFP176 | 87             |

| PQFP208 | 103            |

| CQFP256 | 67             |

Table B-12. A32200DX

| Package | SDO Pin Number |

|---------|----------------|

| CQFP208 | 103            |

| PQFP208 | 103            |

| RQFP208 | 106            |

| RQFP240 | 123            |

| CQFP256 | 67             |

Table B-13. A32300DX

| Package | SDO Pin Number |

|---------|----------------|

| RQFP208 | 106            |

| RQFP240 | 123            |

| CQFP256 | 67             |

Tables B-14 and B-15 show SDO pin numbers for the A42MX family.

Table B-14. A42MX09

| Package | SDO Pin Number |

|---------|----------------|

| PLCC84  | 52             |

| PQFP100 | 52             |

| VQFP100 | 50             |

| PQFP160 | 82             |

| TQFP176 | 87             |

Table B-15. A42MX16

| Package | SDO Pin Number |

|---------|----------------|

| PLCC84  | 52             |

| PQFP100 | 52             |

| VQFP100 | 50             |

| PQFP160 | 82             |

| TQFP176 | 87             |

| PQFP208 | 103            |

Tables B-16 through B-19 show pin numbers for the RH/RT devices.

Table B-16. RT1280A/RH1280

| Package | SDO Pin Number |

|---------|----------------|

| CQFP    | 172            |

Table B-17. RT1425A

| Package | SDO Pin Number |

|---------|----------------|

| CQFP132 | 63             |

Table B-18. RT1460A

| Package | SDO Pin Number |

|---------|----------------|

| CQFP196 | 99             |

Table B-19. RT14100A

| Package | SDO Pin Number |

|---------|----------------|

| CQFP256 | 126            |

#### Note:

ACT1 and 40MX families of devices do not contain SDO pin. PRA from the device must be connected to SDO input of Silicon Explorer.

For devices not listed (i.e. 42MX24/A42MX36, SX, eX, SX-A, RTSX, RTSX-S, and AX), they do not contain SDO pin, but instead a TDO pin. Please check the "Package Pin Description" section of the appropriate datasheet at <a href="http://www.actel.com/techdocs/ds/">http://www.actel.com/techdocs/ds/</a>.

# **Troubleshooting**

The following is a list of frequently asked questions for Silicon Explorer II. For more information, visit the Actel online support website at http://www.actel.com/guru. This chapter is divided into four sections:

- Errors and troubleshooting

- General information

- Software setup

- Hardware setup

## **Errors and Troubleshooting**

- Q: I've connected Silicon Explorer II and the window display reads N/C. Why?

- A: Look on the top of the Silicon Explorer II for the flashing yellow "heartbeat." If it isn't flashing make sure you have properly connected an adequate power supply.

- Q: It's flashing but still N/C. Why?

- A: There are a number of things that prevent you from establishing communication. The following are the most common:

- Wrong COM port. Try all four COM ports, even if you are sure that your mouse is on COM 1.

- No power to Silicon Explorer II (see above).

- Desktop Systems External connector not connected to the COM port internally.

- Laptop systems external COM connector disabled (IR Port Override?). Use your PC's CMOS setup program to enable the COM port.

- COM port IRQ reassigned for DOS program, control panel not updated.

- Multiple mouse drivers in system.ini.

- Third-party serial port "enhancers" do not conform to windows API.

- Q: I've got the IDLE message, but when I click on Run, the Silicon Explorer II window flashes an error message and returns to IDLE. Why?

- A: If the target power is incapable of supplying the necessary current, then Silicon Explorer II resets and returns to IDLE. Many current-limiting supplies will trip when set too close to the operating current.

- Q: The Analyze module acquires data and then indicates errors on read-back. Why?

#### **Errors and Troubleshooting**

- A: The Analyze module bursts data back in blocks at high speeds, with built-in retry for a bad block (it uses both checksum and byte count). Some third-party serial programs block all interrupts, forcing the analyzer into a retry loop.

- Some laptops power down the UART and drop a few characters. Try disabling "Power Saving" in the CMOS setup menu.

- Q: When the Explore window is open, my other Windows programs run slowly. Why?

- A: If the Explore window is open but not connected or powered up, then the system is constantly timing out looking for a response. Either close the SE II window or change the COM port to DEMO.

- Q: I get a message "Device Timed out" when I try to assign a particular signal to the Probe pins. Why?

- A: This message gives us an indication that the power is not sufficient for the Silicon Explorer and as a solution you would have to add a separate power source for the Silicon Explorer. Refer to "Powering Silicon Explorer II" on page 7 for more information.

- Q: I have assigned an internal signal to PRA and PRB but the PRA and PRB light is not blinking on the Probe Pilot. Is this normal?

- A: The PRA and the PRB light on the Probe Pilot are just an indication of the logic level of that assigned internal signal. If the assigned internal net is at permanent logic 0, the light on the Probe Pilot for the corresponding probe will not glow.

- Q: My cable does not have the TMS and the SDO pins. Why?

- A: Your cable will not have the TMS and the SDO pins if it was bought before the SX probing capability was introduced. To order a new cable (Si-Ex-Ribbons), contact Actel customer service at Customer.Service@actel.com.

- Q: Is the Silicon Explorer displaying an incorrect signal?

- A: Make sure that the signal is sampled at a sufficiently high frequency. The sampling rate should be at least twice the frequency of the fastest changing signal. The maximum frequency at which the signal can be sampled is 100 MHz which limits the frequency of the device to 50MHz. If a higher sampling frequency is required than the PRA and the PRB pins can be connected to a logic analyzer to view the signals.

- Q: Why can't I find the net I wish to probe?

- A: Silicon Explorer lists only the signals which are actually present on the device. There is a possibility that the net which you wish to probe has been optimized in Designer. Please

## **Errors and Troubleshooting**

check the list of the nets combined in the combiner file (\*.cob) which is exported from Designer File>Export>Auxillary File with file type \*.cob

#### General Information

- Q: What are the limitations in probing Actel devices using Silicon Explorer?

- A: Probing limitations are described in Table C-1. Note that -- indicates that the feature is unavailable, and \* indicates that the feature only applies to devices that have Qclock.

| Family                  | Probe Capable |       |        |        |  |

|-------------------------|---------------|-------|--------|--------|--|

|                         | Input         | Clock | Hclock | Qclock |  |

| ACT1 <sup>a</sup> /40MX | Y             | Y     |        |        |  |

| ACT2/XL/42MX            | Y             | Y     |        |        |  |

| ACT3                    | Y             | Y     | Y      |        |  |

| DX/42MX                 | Y             | Y     |        | Y*b    |  |

| SX/SX-A/eX              | N             | Y     | N      | N*c    |  |

Table C-1. Probing Limitations

- a. For old ACT1 devices (specifically A10xx, A10xxA, some A10xxB, all TI material, and Military ACT1) the probed signal is inverted. We do not have a specific break point in the lot numbers for A10xxB devices, however if you provide the lot number to us, we will try to determine if that lot has inverted probe signals. Of course the best way to know for sure is to probe the output of an input buffer and compare the Silicon Explorer reading with the applied value.

- b. QCLKINT signal is inverted and may be swapped with an adjacent quadrant as described in the following Guru document: http://www.actel.com/apps/guru/oct98/hw1668.html

- c. QClock probe ability for SX72A/SX72S is currently disabled but may become available in the future.

## **General Information**

- Q: Does Silicon Explorer support ProASIC programming and debugging?

- A: No. As of today Silicon Explorer does not support either ProASIC programming or debugging.

- Q: What are the accessories available for the Silicon Explorer?

- A: Silicon Explorer Accessories:

- SI-EX-RIBBONS: Ribbon and breakout cables for FPGA probe connection

- SI-EX-TCA: Flying lead cable assembly

- Quick Probe Clips

- Q: Can we use Silicon Explorer to debug devices which have their security fuses programmed?

- A: As a part of the Actel FPGAs security feature the Silicon Explorer cannot be used on devices which have their security fuse programmed.

- Q: Can I use the probe pins as regular I/Os?

- A: All of the probe pins can be used as user I/O except for the MODE and TMS pins. Once the device enters probe mode, The I/O's switch to the probe functionality. We highly recommend that you do not use these pins as inputs, since your device will not accept the inputs during probe mode.

- Q: What are the differences between Silicon Explorer I and Silicon Explorer II?

- A: The main difference between Silicon Explorer I and Silicon Explorer II is that the Silicon Explorer II logic-analysis system was enhanced to support an external power supply, which permits internal probing of 5.0V, 3.3V, and 2.5V FPGAs. Other features include four-levels of triggering, decompression on download to speed up response time and system acquisition rates up to 100MHz.

## **Software Setup**

- Q: How do I set up triggering?

- A: You have an option of setting trigger either EARLY that displays the values in the ratio of (25% 75%), where the first % represents the % of data sampled before the trigger point and the later % represent % sampled after the trigger point. The other options available are CENTER(50% 50%) and LATE(75% 25%). You can select the trigger position from Instrument -> Trigger Position and then selecting the required Trigger position.

- Q: What is the recommended sampling rate?

- A: For an accurate reading, the sampling rate for a particular signal should be at least twice the rate at which the signal is changing (According to the Nyquist theorem).

#### Hardware Setup

For example, a clock operating at 25MHz should be sampled at least 50MHz frequency. Sampling at higher frequencies however causes the Silicon Explorer to consume more power.

- Q: What is the best way to find nets?

- A: The best way to find the nets in the Silicon Explorer is to use the Filter option available in the software. You can search for the net you require by using the \*partial\_name\* in the filter, which would return all the signals having that partial\_name of the net. If you are using an HDL flow, it may be difficult to recognize the net names you need to observe. We recommend that you use a synthesis tool that can generate a gate-level schematic of your synthesized netlist so that during probing, you can easily trace through the schematic and obtain the net names from it.

## **Hardware Setup**

- Q: How do I probe an SX-A device?

- A: The probing of an SXA device requires special setup because it requires a 70 ohm termination on all the probe connectors (TDI, TDO, TCK, TMS, PRA, PRB). The 70 ohm series termination is used to prevent data transmission corruption during probing.

- Q: How do I tie the TRST pin during the probing using Silicon Explorer?

- A: TRST is an active low input. During JTAG mode and Silicon Explorer debugging mode, JTAG state machine's reset must not be active, otherwise probe circuitry is disabled. Below is the recommendation for TRST pin in JTAG and Silicon Explorer:

- RTSX Rev0 No TRST pin

- RTSX Rev1 You must tie TRST pin high when doing JTAG and Silicon Explorer

- RTSX Rev2 You can leave the TRST pin floating (or drive it high it must not be driven low) when running JTAG or Silicon Explorer if "Reserve JTAG TRST" was selected in Designer.

- SXA You can leave the TRST pin floating when running JTAG or Silicon Explorer

- Q: What are the different options that I have to connect a device to Silicon Explorer Probe Pilot?

- A: You can connect the Silicon Explorer to the device by either implementing a probe connector on the board for use with the ribbon connector or by connecting the device to the Probe-Pilot using the flying lead connector. If you choose the second alternative, you

#### Hardware Setup

- can either use posts on your board, or the clips provided with the Si Explorer to connect directly to the probe pins. Please refer to question 16 for information about the probe connector dimensions.

- Q: Where can I get the mechanical dimensions for the Silicon Explorer's Probe connector?

- A: Please refer to the following guru document for detailed information about the connector. http://www.actel.com/GURU\_docs/feb00/ns853.html.

- Q: Where can I find the pin layout of the Silicon Explorer?

- A: The pin layout for the Silicon Explorer is found on the back of the Silicon Explorer case. There is a notch on one side of the pin connector that determines the position of Pin 1.

- Q: How is the checksum of the device read?

- A: The checksum of most devices is read through the TDO/SDO pin. For information about the location of SDO pins in all Actel Devices please refer to "Location of the SDO Pins" on page 29.

- ACT1 and the 40MX pins do not have an SDO pin. In order to read the checksum from ACT1/40MX devices the PRA on the device must be connected to the SDO pin of the Silicon Explorer.

- Q: What are the power requirements for Silicon Explorer II?

- A: Silicon Explorer II must be connected to a power supply of 5V for 5V tolerant devices, 3.3V for 3.3V tolerant devices, and 2.5V for 2.5V tolerant devices.

Hardware Setup

# Index

| A                          | Probe Leads, Connecting 5 |

|----------------------------|---------------------------|

| Analyze Module 13          | Probe Pilot 33            |

| View Data 15               | Probing                   |

|                            | Software 10               |

| C                          |                           |

| Checksum Error Messages 12 | S                         |

| Command Module 10          | Sampling Rate 32          |

| Explore FPGA 10            | SDO Pin Location 21       |

| Export a Probe File 11     | Security Fuses 31         |

| Probing a Node 12          | Settings, Software 2      |

| Connecting 2, 3            | Silicon Explorer          |

| ACT1/A40MX Devices 6       | Connecting 2, 3           |

| Connector Types 4          | Powering 3                |

| Current Consumption 4      | Software Settings 2       |

|                            | Software                  |

| D                          | Command Module 10         |

| Demo Mode 2                | System Requirements 2     |

| _                          | T                         |

| <u>E</u>                   | Triggering, Setup 32      |

| Explorer Software          | ringgering, Setup 32      |

| Analyze Module 13          |                           |

| Exporting, Probe Files 11  |                           |

| F                          |                           |

| Flexible JTAG Mode 19      |                           |

|                            |                           |

| L                          |                           |

| Logic Analysis 5           |                           |

| 5                          |                           |

| P                          |                           |

| Pin Layout 33              |                           |

| Power Configurations 3     |                           |

| Power Source 3             |                           |

| ProASIC Support 31         |                           |

| Probe Connector, Pin-Out 5 |                           |