# Designer v6.1 User's Guide

### Actel Corporation, Mountain View, CA 94043

© 2004 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 5029122-10

Release: October 2004

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

### **Trademarks**

Actel and the Actel logotype are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

Mentor Graphics, Precision RTL, Exemplar Spectrum, and Leonoardo Spectrum are registered trademarks of Mentor Graphics, Inc.

WaveFormerLite is a registered trademark of SynaptiCAD, Inc.

Synplify is a registered trademark of Synplicity, Inc.

Sun and Sun Workstation, SunOS, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc

Synopsys is a registered trademark of Synopsys, Inc.

Verilog is a registered trademark of Open Verilog International.

Viewlogic, ViewSim, ViewDraw and SpeedWave are trademarks or registered trademarks of Viewlogic Systems, Inc.

Windows is a registered trademark and Windows NT is a trademark of

Microsoft Corporation in the U.S. and other countries.

UNIX is a registered trademark of X/Open Company Limited.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

## **Table Of Contents**

| Welcome to Designer                                 |

|-----------------------------------------------------|

| Starting Designer                                   |

| Back-Annotation5                                    |

| Starting a New Design                               |

| Opening An Existing Design                          |

| Opening Designs Created in Previous Versions        |

| Opening Locked Files                                |

| Starting Other Applications from Designer (Pc Only) |

| About Your Installation10                           |

| Directory Preferences10                             |

| Updates10                                           |

| Proxy11                                             |

| File Association (Pc Only)                          |

| Setting Your Log Window Preferences                 |

| PDF Reader (UNIX Only)                              |

| Web Browser (UNIX only)                             |

| Device Selection Wizard                             |

| Setting Die, Package, Speed, And Voltage            |

| Device Variations                                   |

| Setting Operating Conditions                        |

| Changing Design Name and Family14                   |

| Changing Device Information                         |

| Importing Source Files                                       | 15 |

|--------------------------------------------------------------|----|

| Auditing Files                                               | 17 |

| Importing Auxiliary Files                                    | 17 |

| Keep Existing Timing Constraints in SDC Files                | 18 |

| Keep Existing Physical Constraints                           | 18 |

| Compiling Your Design                                        | 19 |

| Setting Compile Options                                      | 19 |

| MX, SX, SX-A, eX Compile Options                             | 19 |

| Axcelerator Compile Options                                  | 20 |

| ProASIC and ProASICPLUS Compile Options                      | 20 |

| ProASIC3/E Compile Options                                   | 20 |

| About Design Constraints                                     | 25 |

| About Location and Region Assignments                        | 25 |

| About Physical Constraints and Attributes                    | 25 |

| Types of Physical Constraints                                | 26 |

| Timing Constraints                                           | 26 |

| Running Layout                                               | 27 |

| Axcelerator Layout Options                                   | 27 |

| ProASIC3/E, ProASICPLUS, and ProASIC Layout Options          | 28 |

| ProASIC3/E, ProASICPLUS, and ProASIC Layout Advanced Options | 29 |

| eX, SX, SX-A Layout Options                                  | 29 |

| eX, SX, and SX-A Advanced Layout Options                     | 30 |

| ACT MX and DX Layout Ontions                                 | 30 |

| ACT, MX, and DX Advanced Layout Options    | 31 |

|--------------------------------------------|----|

| Incremental Placement                      | 31 |

| Multiple Pass Layout                       | 32 |

| Analyzing Timing in Your Design            | 33 |

| Analyzing Power Consumption in Your Design | 33 |

| Viewing Your Netlist                       | 33 |

| Back-Annotation                            | 33 |

| Available Report Types                     | 35 |

| Status Reports                             | 35 |

| Timing Reports                             | 36 |

| Pin Reports                                | 36 |

| Flip-Flop Reports                          | 37 |

| Power Reports                              | 37 |

| Timing Violations Reports                  | 38 |

| I/O Bank Reports                           | 38 |

| Exporting Files                            | 41 |

| Saving Your Design                         | 43 |

| Exiting Designer                           | 43 |

| About Tcl Commands                         | 45 |

| Tcl Documentation Conventions              | 47 |

| backannotate                               | 48 |

| close_design                               | 50 |

| compile                                    | 51 |

| export                                                | 56 |

|-------------------------------------------------------|----|

| extended_run_shell                                    | 56 |

| get_defvar                                            | 58 |

| get_design_filename                                   | 59 |

| get_design_info                                       | 60 |

| import_aux                                            | 62 |

| import_source                                         | 63 |

| is_design_loaded                                      | 66 |

| is_design_modified                                    | 67 |

| is_design_state_complete                              | 67 |

| layout                                                | 69 |

| layout (Advanced Options for the SX family)           | 70 |

| layout (Advanced Options for ProASIC and ProASICPLUS) | 71 |

| layout (Advanced options for Axcelerator)             | 73 |

| new_design                                            | 75 |

| open_design                                           | 76 |

| pin_assign                                            | 77 |

| pin_commit                                            | 80 |

| pin_fix                                               | 80 |

| pin_fix_all                                           | 81 |

| pin_unassign                                          | 82 |

| pin_unassign_all                                      | 83 |

| pin_unfix                                             | 83 |

| report                          | 84  |

|---------------------------------|-----|

| save_design                     | 84  |

| set_design                      | 85  |

| set_device                      | 86  |

| set_defvar                      | 88  |

| smartpower_add_pin_in_domain    | 89  |

| smartpower_commit               | 90  |

| smartpower_create_domain        | 90  |

| smartpower_remove_domain        | 91  |

| smartpower_remove_pin_frequency | 92  |

| smartpower_remove_pin_of_domain | 93  |

| smartpower_restore              | 94  |

| smartpower_set_domain_frequency | 94  |

| smartpower_set_pin_frequency    | 96  |

| timer_add_clock_exception       | 96  |

| timer_add_pass                  | 97  |

| timer_add_stop                  | 98  |

| timer_commit                    | 99  |

| timer_get_path                  | 99  |

| timer_get_clock_actuals         | 102 |

| timer_get_clock_constraints     | 102 |

| timer_get_maxdelay              | 103 |

| timer get path constraints      | 104 |

| timer_remove_clock_exception10                                             | )4         |

|----------------------------------------------------------------------------|------------|

| timer_remove_pass10                                                        | )5         |

| timer_remove_stop10                                                        | )6         |

| timer_restore                                                              | )6         |

| timer_setenv_clock_freq10                                                  | ) <b>7</b> |

| timer_setenv_clock_period10                                                | )8         |

| timer_set_maxdelay10                                                       | )8         |

| timer_remove_all_constraints11                                             | 10         |

| About Design Constraints                                                   | 10         |

| Designer Naming Conventions                                                | l <b>1</b> |

| Location and Region Assignment Constraints11                               | l <b>1</b> |

| I/O Assignment Constraints11                                               | 12         |

| Attributes11                                                               | 12         |

| Overview - Entering Constraints                                            | <b>12</b>  |

| Assigning I/O Constraints11                                                | 13         |

| Assigning Location and Region Constraints11                                | 13         |

| About Physical Design Constraint (PDC) Files11                             | <b>14</b>  |

| Importing PDC Files (ProASIC3E, ProASIC3, and Axcelerator Families Only)11 | 15         |

| Types of Constraints                                                       | 16         |

| ProASIC and ProASICPLUS Timing Constraints11                               | 16         |

| GCF to SDC Timing Constraints Conversion11                                 | l <b>7</b> |

| GCF Syntax Conventions                                                     | l <b>7</b> |

| Synopsys Design Constraints (SDC) Files                                    | 18         |

| About DCF Files119                                |

|---------------------------------------------------|

| DCF Syntax Rules                                  |

| About PIN Files                                   |

| I/O Standards Compatibility Matrix122             |

| I/O Standards And I/O Attributes Applicability122 |

| GCF Constraint Quick Reference                    |

| Priority Order for Global Promotion124            |

| dont_fix_globals124                               |

| read                                              |

| set_auto_global125                                |

| set_auto_global_fanout                            |

| set_global125                                     |

| set_noglobal125                                   |

| use_global                                        |

| Netlist Optimization Constraints                  |

| Netlist Optimization Constraint Syntax128         |

| dont_optimize128                                  |

| dont_touch128                                     |

| optimize                                          |

| set_max_fanout128                                 |

| Placement Constraints                             |

| Macro                                             |

| Package Pin and Pad Location                      |

| net_critical_ports                           | 131 |

|----------------------------------------------|-----|

| set_critical                                 | 131 |

| set_critical_port                            | 131 |

| set_empty_io                                 | 131 |

| set_empty_location                           | 131 |

| set_initial_io                               | 132 |

| set_initial_location                         | 132 |

| set_io                                       | 133 |

| set_io_region                                | 133 |

| set_location                                 | 133 |

| set_memory_region                            | 134 |

| set_net_region                               | 134 |

| create_clock                                 | 135 |

| generate_paths                               | 135 |

| set_false_path                               | 135 |

| set_input_to_register_delay                  | 136 |

| set_max_path_delay                           | 136 |

| set_multicycle_path                          | 136 |

| set_register_to_output_delay                 | 136 |

| About Physical Design Constraint (PDC) Files | 137 |

| PDC Syntax Conventions                       | 138 |

| PDC Naming Conventions                       | 140 |

| assign global clock                          | 141 |

| assign_local_clock                  | 142 |

|-------------------------------------|-----|

| assign_net_macros                   | 142 |

| assign_region                       | 143 |

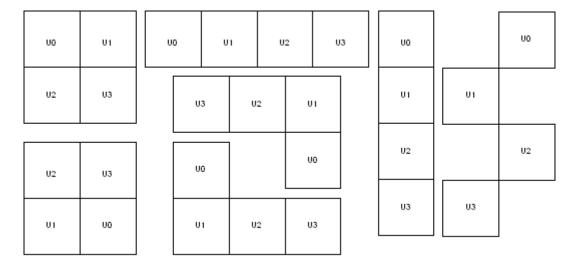

| define_region (rectangular region)  | 144 |

| define_region (rectilinear region)  | 145 |

| delete_buffer_tree                  | 146 |

| dont_touch_buffer_tree              | 147 |

| move_region                         | 148 |

| reset_floorplan                     | 148 |

| reset_io                            | 149 |

| reset_iobank                        | 150 |

| reset_net_critical                  | 151 |

| set_io                              | 152 |

| set_iobank                          | 152 |

| set_location                        | 152 |

| set_multitile_location (ProASIC3/E) | 153 |

| set_net_critical                    | 156 |

| set_vref                            | 157 |

| set_vref_defaults                   | 158 |

| unassign_global_clock               | 158 |

| unassign_local_clock                | 159 |

| unassign_macro_from_region          | 160 |

| unassign net macro                  | 161 |

| undefine_region                                          | 161 |

|----------------------------------------------------------|-----|

| Design Object Access Commands                            | 162 |

| get_clocks                                               | 162 |

| get_pins                                                 | 163 |

| get_ports                                                | 163 |

| all_inputs                                               | 163 |

| all_outputs                                              | 164 |

| create_clock (SDC clock constraint)                      | 164 |

| set_false_path (SDC false path constraint)               | 165 |

| set_load (SDC load constraint)                           | 166 |

| set_max_delay (SDC max path constraint)                  | 166 |

| set_multicycle_path (SDC multiple cycle path constraint) | 167 |

| SDC Command Limitations                                  | 168 |

| global_clocks                                            | 169 |

| max_delays/min_delays                                    | 169 |

| io_arrival_times                                         | 170 |

| global_stops                                             | 171 |

| pin_loads                                                | 171 |

| I/O Attributes by Family                                 | 171 |

| Bank Name                                                | 172 |

| Hot Swappable                                            | 172 |

| Input Delay                                              | 172 |

| I/O Standard                                             | 173 |

| I/O Threshold               | 176 |

|-----------------------------|-----|

| Locked                      | 176 |

| Macro Cell                  | 177 |

| Output Drive                | 177 |

| Output Load or Loading (pf) | 178 |

| Pin Number                  | 178 |

| Port Name                   | 179 |

| Power-Up State              | 179 |

| Resistor Pull               | 179 |

| Schmitt Trigger             | 180 |

| Skew                        | 181 |

| Slew                        | 181 |

| Use Register                |     |

| Actel Headquarters          |     |

| Technical Support           |     |

| Customer Service            |     |

| Index                       |     |

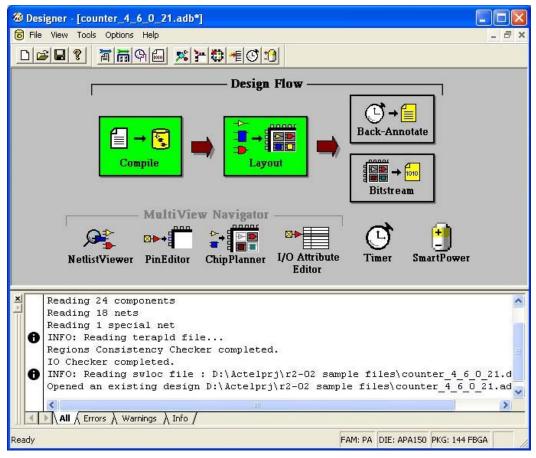

## Welcome to Designer

The Designer interface offers both automated and manual flows, with the push-button flow achieving the optimal solution in the shortest cycle.

The basic steps to implement your design include:

Starting a new design\*

Importing your source and auxiliary file(s)\*

Compiling your design

Running Layout to place-and-route your design

Back-Annotating your design

Generating your programming file (Fuse or Bitstream)

Programming your device

Designer also includes the following User Tools that can be used to optimize your design:

PinEditor package level floorplanner and I/O attribute editor

ChipEditor chip level module placer

ChipPlanner floorplanning tool

NetlistViewer design schematic viewer

SmartPower power analysis tool

Timer static timing analysis and constraints editor

Timing driven place and route

ACTgen macro generator

These tools give you the flexibility to drive the place-and-route tools and meet your design requirements.

## **Starting Designer**

To start standalone Designer:

### On a PC

Click Start, point to the Programs menu and click Designer.

### **UNIX**

Type the following command at the prompt:

<location of Actel software>/bin/designer

Designer opens and is ready for you to initiate your Designer Session.

## **Back-Annotation**

The back-annotation functions are used to extract timing delays from your post layout data. These extracted delays are put into a file to be used by your CAE package's timing simulator. If you wish to perform pre-layout back-annotation, select Export and Timing Files from the File menu.

The Back-Annotation command creates the files necessary for back-annotation to the CAE file output type that you chose. Refer to Actel Interface Guides or the documentation included with your simulation tool for information about selecting the correct CAE output format and using the back-annotation files.

#### To back-annotate your design:

- 1. From the **Tools** menu, click **Back-Annotate**, or click the Back-Annotate button in the Design Flow window.

- 2. Make your selections in the Back-Annotate dialog box and click **OK**.

**Extracted Files Directory:** The file directory is your default working directory. If you wish to save the file elsewhere, click Browse and specify a different directory.

**Extracted File Names:** This name is used as the base-name of all files written out for back-annotation. Do not use directory names or file extensions in this field. The file extensions will be assigned based on your selection of which file formats to export. The default value of this field is <design>\_ba.

Output Formats: Select the file format of the timing file. One of SDF or STF.

(STF is only supported for ACT1, ACT2, ACT3, DX, MX, SX).

Simulator Language: Select either Verilog or VHDL93.

**Export Additional Files:** Check Netlist or Pin to export these files at the same time. For Axcelerator, ProASIC3, and ProASIC3E, you must export and use the 'flattened' netlist (AFL-style) with the back-annotated timing file (SDF) in timing simulation.

Note: For Axcelerator, ProASIC3, and ProASIC3E, you cannot select SDF format using File -> Export Files -> Timing.

You have no choice regarding exporting the netlist from the back-annotate command for Axcelerator, ProASIC3, and ProASIC3E. This selection is hard-coded to be 'on'. For all other families, the export-netlist and back-annotate generates equivalent netlist files. So the back-annotate command does not enforce the writing out of the netlist during back-annotate.

## Starting a New Design

To begin a new design session, you must start a new design or open an existing design.

Starting a new design creates an Actel ADB file. ADB files are proprietary Actel project files.

### To start a new design:

- 1. Click **Start New Design** in the Designer main window, or in the **File** menu, click **New**. This displays the Setup Design dialog box.

- 2. Setup Design:

Enter a **Design Name**. The design name is used in reports and as the default name when saving or exporting files.

Select an Actel Family from the drop down menu list.

Specify a working directory. Click Browse to locate a directory.

3. Click **OK**. The Designer custom design flow window appears. All tools and commands are activated.

Designer:New Design

## **Opening An Existing Design**

#### To open an existing design:

- 1. Click **Open Existing Design** or in the **File** menu, click **Open**. This displays the Open dialog box.

- 2. Select File. Type the full path name of the .adb file in the File Name box, or select the file from the list.

- 3. Click Open. Designer's custom design flow window appears and all tools and commands are activated. When you open an existing design, Designer checks to see if you have modified your netlist since the last time you imported the netlist into this design. If you have, Designer prompts you to re-import your netlist.

## **Opening Designs Created in Previous Versions**

Designer can directly open designs created with previous versions of the Designer software.

If your design was created in version 3.1 or earlier, contact Applications or go to <a href="http://www.actel.com/support">http://www.actel.com/support</a> for information on converting your design.

All existing die, package, pin assignments, and place-and-route information is read and maintained. Designs created in previous versions of software may need library conversions when loaded into the Designer environment. If your design requires this conversion, Designer prompts you to allow the software to update the design to the new library before you attempt to start any of the Designer features.

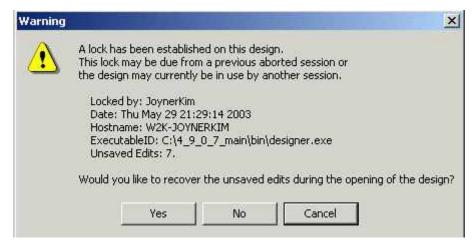

## **Opening Locked Files**

Designer notifies you if a lock has been established on your file. You might get a warning or an error message when opening a design with a lock.

### Warning

Designer warns you when opening a design that was not closed properly or may be open somewhere else. You can choose to recover the unsaved edits.

Warning: Locked File

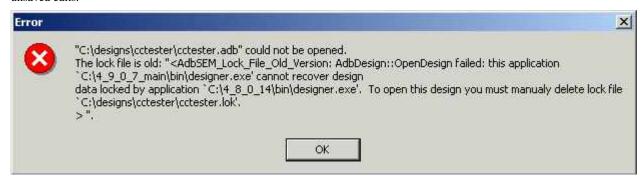

### **Error**

When opening a design, an error might notify you that the file can't be opened because the lock file is old. You can't recover any unsaved edits.

Error: Locked File

### To open a design with an old lock file:

- 1. Go to the design directory.

- 2. Locate the design .adb file and corresponding .lok file.

- 3. Delete the .lok file.

- 4. Return to Designer and open the design.

| Name         | Size  | Туре                | Modified            |

|--------------|-------|---------------------|---------------------|

| ada01928.4   | 87 KB | 4 File              | 2/7/2003 10:24 PM   |

| cctester.adb | 87 KB | Actel Designer Desi | 12/11/2001 10:39 AM |

| cctester.lok | 1 KB  | LOK File            | 2/7/2003 10:24 PM   |

## Starting Other Applications from Designer (Pc Only)

You can start any application from Designer that you have added to the Tools menu.

### To add an application to the Tools menu:

- 1. From the Tools menu, click Customize.

- 2. Enter the application name in the Menu Text area. This text will appear in the Tools command menu.

- 3. Enter the command to execute, or click the Browse button to select an executable filename. If the location of the command to execute is not in your path, you must include the absolute path when specifying the command.

- 4. In the Arguments text box, enter the command-line arguments that will be passed to the command when executing.

- 5. In the Initial Directory field, type the absolute path of the directory in which the application will initially be executed.

- Click Add.

- 7. When you are finished adding tools, click **OK**. The application name you added appears in the Tools menu.

#### To remove an application from the Tools menu:

- 1. From the Tools menu, click Customize.

- 2. Select the application to remove and click Remove.

3. When you are finished removing applications, click OK.

#### To order applications in the Tools menu:

- 1. From the **Tools** menu, click Customize.

- 2. Reorder the tools by selecting one at a time and clicking the Move Up or Move Down buttons.

- Click OK when you are finished. The tools will appear in the Tools menu in the same order as they do in the Menu Contents list box.

## **About Your Installation**

#### To display information about your license:

From the Start menu, click Programs, and then click the Actel software folder and select About Your Installation. The software displays your complete license configuration, all Actel-installed software and versions, as well as your HostID and disk volume serial number.

You can also select License Details from the Help menu in Designer to view your license information.

## **Directory Preferences**

When executing a command or function such as Open or Save, Designer uses the directory you specify as the start-up directory.

### To specify your directory preferences:

- 1. From the File menu, click Preferences.

- Click the **Directory** tab.

- 3. Specify your Startup directory.

- 4. Select your working directory options:

- 5. To design file's directory when opening design: Select to automatically change directories when opening a design.

- 6. To design file's directory when saving design: Select to automatically change directories when saving a design.

- 7. To script file's directory when executing script: Select to automatically change directories when executing a script.

- 8. **Add design name to working directory when creating design**: Select to enable a design name folder to be automatically created in the working directory when creating a new design.

- 9. Click OK.

## **Updates**

The Updates tab in the Preferences dialog box allows you to set your automatic software update preferences.

#### To set your automatic software update preferences:

- From the File menu, click Preferences and Updates.

- 2. Choose one of the following options and click OK.

- 3. Automatically check for updates at startup: Select to be notified of updates when you start Designer.

- 4. Remind me to check for updates at startup: Select to be asked if you want to check for a software update when you start Designer.

5. Do not check for updates or remind me at startup: Select if you do not want to check for software updates at startup.

To manually check for software updates, from the Help menu, click Check for Software Updates.

**Note:** This feature requires an internet connection.

## **Proxy**

A Proxy improves access to the Actel server.

#### To enable the proxy:

- 1. Select I use a proxy.

- 2. Type the proxy name in the text field.

- 3. Click OK.

## File Association (Pc Only)

Several programs, including Designer, create files with the .adb extension.

Use the File Association tab in the Preferences dialog box to specify Designer as the default program for files with the .adb extension. Doing so starts Designer whenever a file with the .adb extension is double clicked.

#### To associated .adb files with the Designer application:

- 1. From the **File** menu, click **Preferences**.

- 2. Select Check the default file association (.adb) at startup to Check the box to associate .adb files with the Designer application. Un-check the box if you do not want Designer to start when clicking a file with the .adb extension.

- 3. Click OK.

## **Setting Your Log Window Preferences**

Errors, Warnings, and Informational messages are color coded in the log window. You can change the default colors by using the log Window tab in the Preferences dialog box.

#### To change colors in the log window:

- 1. From the **File** menu, choose **Preferences**.

- 2. Click the Log Window tab in the Preferences Dialog Box.

- 3. Select your new default colors and click **OK**.

The default color settings for the log window are:

| Message Type  | Colors     |

|---------------|------------|

| Errors        | Red        |

| Warnings      | Light Blue |

| Informational | Black      |

| Linked        | Dark Blue  |

The default preference is to Clear log window automatically. This clears the Designer log window each time you close or open a new design in Designer. Uncheck the box if you want Designer to leave the log information after you close a design.

## PDF Reader (UNIX Only)

Use the PDF Reader tab to bring up the Designer online manuals. Enter the default reader's name with the full path or click browse.

## Web Browser (UNIX only)

Specify the default web browser you wish to use on the UNIX platform. The web browser displays the online help for Designer.

### **Device Selection Wizard**

After you import your source files, the Device Selection Wizard helps you specify the device, package, and other operating conditions. You must complete these steps before your netlist can be compiled.

The wizard steps include:

Selecting die, package, speed, and voltage

Selecting variations (reserve pins and I/O attributes)

Setting operating conditions

## Setting Die, Package, Speed, And Voltage

The first screen in the <u>Device Selection Wizard</u> allows you to set die, package, speed, and voltage.

- 1. In the **Tools** menu, click **Device Selection** to start the Device Selection Wizard.

- 2. Select **Die** and **Package**. Select a die from the Die list. Available packages are listed for each die.

- Specify Speed.

- 4. Select **Die Voltage**. Select from the available settings in Die Voltage drop-down menu. Two numbers separated by a "/" are shown if mixed voltages are supported. If two voltages are shown, the first number is the I/O voltage and the second number is the core (array) voltage.

- 5. Click **Next** to set reserve pins and I/O Attributes.

## **Device Variations**

The second screen in the Device Selection Wizard enables you to set reserve JTAG and probe pins and the default I/O standard.

#### To select reserve pins and default I/O standard:

- 1. Select your reserve pins:

- 2. Check the Reserve JTAG box to reserve the JTAG pins "TDI," "TMS," "TCK," and "TDO" during layout.

- 3. Check the Reserve JTAG Reset box to reserve the JTAG reset Pin "TRST" during layout.

- 4. Check the Reserve Probe box to reserve the Probe pins "PRA," "PRB," "SDI," and "DCLK" during layout.

Reserve Pins are not selectable for the Axcelerator, ProASIC, and ProASIC Plus families.

5. Select an I/O attribute. The I/O Attributes section notifies you if your device supports the programming of I/O attributes on a perpin basis. For the Axcelerator family, the I/O Attribute section allows you to set the default I/O standard for the I/O banks.

6. Click Next to set operating conditions.

## **Setting Operating Conditions**

Operating Conditions, step 3 of the <u>Device Selection Wizard</u>, enables you to define the voltage and temperature ranges a device encounters in a working system. The operating condition range entered here is used by Timer, the timing report, and the back-annotation function. These tools enable you to analyze worst, typical, and best case timing.

### **Junction Temperature**

Select a junction temperature. Supported ranges include:

Commercial (COM)

Industrial (IND)

Military (MIL)

Automotive

Custom

Consult the Actel Data Sheet, available at <a href="http://www.actel.com/techdocs/ds/index.html">http://www.actel.com/techdocs/ds/index.html</a> to find out which temperature range you should use.

If you select Custom, edit the Best, Typical, and Worst fields. Modify the range to the desired value (real) such that Best < Typical < Worst.

You can calculate junction temperature from values in the Actel Data Sheet, available at <a href="http://www.actel.com/techdocs/ds/index.html">http://www.actel.com/techdocs/ds/index.html</a>.

The temperature range represents the junction temperature of the device. For commercial and industrial devices, the junction temperature is a function of ambient temperature, air flow, and power consumption.

For military devices, the junction temperature is a function of the case temperature, air flow, and power consumption. Because Actel devices are CMOS, power consumption must be calculated for each design. For most low power applications (e.g. 250mW), the default conditions should be adequate.

Performance decreases approximately 2.5% for every 10 degrees C that the temperature values increase. Refer to the SmartPower online help for more information about power consumption.

## **Voltage**

Select a voltage:

Commercial (COM)

Industrial (IND)

Military (MIL)

Automotive

Custom

If you select Custom, you may choose from Best > Typical > Worst in the drop-down menu.

### **Radiation Derating**

Conservative post radiation performance estimates are available for some radiation tolerant devices based upon the number of KRads the device is expected to be subjected to. Radiation effects vary by device lot and may not be completely representative of the lot you are using. Post radiation timing numbers are only meant to be a guide and are not a guarantee of performance. Customers must consult the specific radiation performance report for the specific lot used. Post radiation exposure estimates currently only affect timing numbers. The SmartPower power analysis tool is not affected by changing the radiation exposure value.

### RTSX-S and RTAX-S ONLY - Radiation Derating

This option is only available for RTSX-S and RTAX-S devices. The valid range is integer values from 0 to 300, and the units are in KRads. Modifying this selection impacts the timing derating in Timer and back-annotating SDF files, so when you modify this value, you must extract a new SDF file from Designer and re-evaluate the timing of your design. It does not affect the device configuration.

## **Changing Design Name and Family**

Design name and family are set when you create a new design. However, you can change this information for existing designs. If you change the family, you must re-import the netlist. Use the following procedure to change the name of a design and the targeted Actel family for the design.

#### To change the design name or family:

- 1. In the **Tools** menu, click **Setup Design**. This displays the Setup Design dialog box.

- 2. Specify the design name and family.

- 3. Click **OK**. Refer to the Actel datasheet for your device for family specifications.

You may wish to migrate your SX device to an SX-A device. The SX to SX-A compatible family change option is available in the Device Selection wizard.

### To migrate your SX design to SX-A:

- 1. Open your SX design.

- 2. From the **Tools** menu, select **Device Selection**.

- 3. Select "SXA" from the **Change to** drop down menu, and proceed in the <u>Device Selection Wizard</u> to complete the migration. You must re-compile and layout your design to run the Designer User Tools.

## **Changing Device Information**

Device and package information, device variations, and operating conditions are set when you import a netlist and compile a new design. However, you can change this information for existing designs.

### To change device information for existing designs:

- 1. In the **Tools** menu, click **Device Selection**. The Device Selection Wizard appears.

- 2. Select Die, Package, and Speed Grade and click Next. (You must select die and package to continue.)

- 3. Select Device Variations and click Next.

- Select Operating Conditions and click Finish.

Refer to the Actel FPGA Data Book or call your local Actel Sales Representative for information about device, package, speed grade, variations, and operating conditions.

### **Compatible Die Change**

When you change the device, some design information can be preserved depending on the type of change.

### **Changing Die Revisions**

If you change the die from one technology to another, all information except timing is preserved. An example is changing an A1020A (1.2um) to an A1020B (1.0um) while keeping the package the same.

### **Device Change Only**

Constraint and pin information is preserved, when possible. An example is changing an A1240A in a PL84 package to an A1280A in a PL84 package.

### **Repackager Function (Non-Axcelerator families only)**

When the package is changed (for the same device), the Repackager automatically attempts to preserve the existing pin and Layout information by mapping external pin names based on the physical bonding diagrams. This always works when changing from a smaller package to a larger package (or one of the same size). When changing to a smaller package, the Repackager determines if any of the currently assigned I/Os are mapped differently on the smaller package. If any of the I/Os are mapped differently, then the layout is invalidated and the unassigned pins identified.

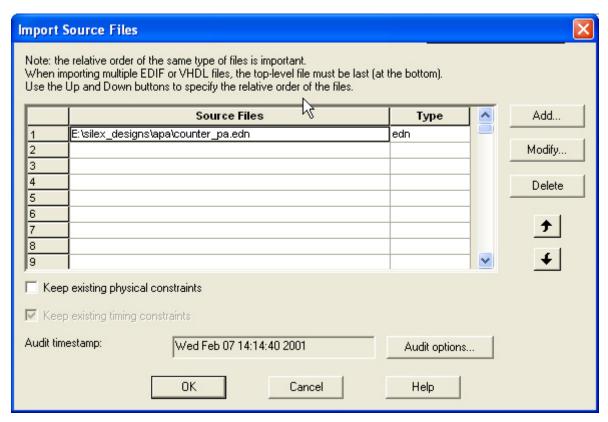

## **Importing Source Files**

Source files include your netlist and constraint files.

Source files are files created by outside tools that will be tracked (audited) to better coordinate the design changes. If you wish, you may import some files as <u>auxiliary files</u>. Auxiliary files are not audited, but you do not have to re-compile your design after you import them.

| Source Files                                              | File Type Extension |

|-----------------------------------------------------------|---------------------|

| EDIF                                                      | *.ed*               |

| Verilog                                                   | *.V                 |

| VHDL                                                      | *.vhd               |

| Actel ADL Netlist                                         | *.adl               |

| Criticality                                               | *.crt               |

| ProASIC Constraint File (ProASIC PLUS, ProASIC)           | *.gcf               |

| Physical Design Constraint File (ProASIC3/E, Axcelerator) | *.pdc               |

| SDC                                                       | *.sdc               |

The choice of source files is family dependent. Only supported source files are displayed in the Import Source dialog box. If you are working on a new design or if you have changed your netlist, then you must re-import your netlist into Designer.

### To import a source file:

1. From the **File** menu, choose **Import Source Files**. This displays the Import Source Files dialog box, as shown in the figure below.

Import Source Files Dialog Box

- 2. Click Add. The Add Source Files dialog appears.

- 3. Select the file you want to import and click Import. The File is added to the Import Source Files dialog box.

- 4. Add more source files to the list. All files added to the Import Source Files dialog box are imported at the same time. To modify a file, select the file and click Modify. To delete a file, select the file and click Delete.

- Specifying a priority is useful if you are importing multiple netlist files, GCF files, or PDC, or SDC files. When importing multiple EDIF or structural HDL files, the top-level file must appear last in the list (at the bottom). Drag your files to specify the import order.

- 6. (Axcelerator, ProASIC, ProASIC PLUS, ProASIC3/E designs only) Select Keep existing physical constraints to preserve all existing physical constraints that you have made using ChipPlanner, PinEditor, or the I/O Attribute Editor.

- 7. (SX-A, eX, Axcelerator, ProASIC<sup>PLUS</sup>, ProASIC3/E) Select Keep existing timing constraints to preserve all the existing timing constraints already in your design, whether coming from the Timer tool or previously imported file. If you import an SDC file and select this option, Designer merges the existing constraints and the constraints contained in the SDC file. In case of a conflict, the new constraint has priority over the existing constraint.

- 8. To set the audit options for these source files, click Audit options and follow the directions in the Audit Options dialog box.

- 9. When you are done adding all your source files, click **OK**. Your source files are imported. Any errors appear in the Designer log window.

Note: Designer may not import file names or paths with spaces. Rename the file or path to remove the spaces, and re-import.

### Importing SDC and GCF Files Simultaneously

If you specify SDC and GCF files in the Import source file dialog, GCF files are imported before SDC files regardless of the order you specify. This means that any timing constraints in GCF are converted before the SDC constraints are applied. For a cleaner flow, Actel recommends that you do not use both SDC and GCF timing constraints. SDC is the recommended format.

## **Auditing Files**

Designer audits your source files to ensure that your imported source files are current. All imported source files are date and time stamped. Designer notifies you if the file is changed. When notified, select the appropriate action and click OK.

#### To change your audit settings:

- 1. From the **File** menu, click **Audit Settings**. The Audit Settings dialog box appears. Audit Timestamp reflects the last time and day that the import source or audit update was successfully done.

- 2. Select the audit check box next to the file to enable auditing.

- Click Change Location to open the "Modify File Location" dialog. The Modify File Location dialog box enables you to specify

the correct path so that the design can find the source file(s)..

- 4. Click **Reset to Current Date Time** to associate the file with the current day and time.

## **Importing Auxiliary Files**

Auxiliary files are not audited and are treated more as one-time data-entry or data-change events, similar to entering data using one of the interactive editors (e.g. PinEditor or Timer).

Some timing constraints (such as multi\_cycle) are not supported in the Timer GUI and must be implemented by importing the SDC file. If you import the SDC file as an auxiliary, you do not have to re-compile your design. However, auditing is disabled when you import auxiliary files, and Designer cannot detect the changes to your SDC file(s) if you import them as auxiliary files.

| Auxiliary Files                             | File Type Extension | Family                                                  |

|---------------------------------------------|---------------------|---------------------------------------------------------|

| Criticality                                 | *.crt               | ACT1, ACT2, ACT3, MX, XL, DX                            |

| PIN                                         | *.pin               | ACT1, ACT2, ACT3, MX, XL, DX, SX, SX-A, eX              |

| SDC                                         | *.sdc               | ProASIC3/E, SX-A, eX, Axcelerator,<br>ProASIC PLUS      |

| Physical Design Constraint                  | *.pdc               | ProASIC3/E and Axcelerator                              |

| Value Change Dump                           | *.vcd               | ProASIC3/E, Axcelerator, ProASIC, ProASIC PLUS          |

| Switching Activity Intermediate File/Format | *.saif              | ProASIC3/E, Axcelerator, ProASIC, ProASIC PLUS          |

| Design Constraint File                      | *.dcf               | Axcelerator, ACT1, ACT2, ACT3, MX, XL, DX, SX, SX-A, eX |

### To import an auxiliary file:

- 1. From the File menu, select Import Auxiliary Files. The Import Auxiliary Files dialog appears,

- 2. Click the Add button. The Add Auxiliary Files dialog box appears.

- Select your file and click Import. The file is added to the Import Auxiliary Files dialog box. Continue to add more auxiliary files to the list. Some formats (like DCF and SDC) are not allowed to be imported in multiple auxiliary files.

Modifying: If you need to modify a selection, select the file row and click Modify

**Deleting**: If you need to delete a file, select the file row and click **Delete**.

**Ordering**:Ordering your auxiliary files. Select and drag your files to specify the import order. Specifying a priority is useful if you are importing multiple PDC files.

- 4. After you are done adding all your Auxiliary files, click **OK**. Your auxiliary files are imported. Any errors appear in Designer's Log Window.

- .vcd and .saif are used by SmartPower for power analysis.

- .crt for backwards compatibility with existing designs only.

File names or paths with spaces may not import into Designer. Rename the file or path, removing the spaces, and re-import.

## **Keep Existing Timing Constraints in SDC Files**

The Keep Existing Constraints check box is designed to support an additional "merge or replace" functionality when you import SDC files.

Select **Keep existing timing constraints** to preserve all existing timing constraints that you have made using the Timer GUI or previously imported file. If you import a SDC file and you have this box selected, Designer merges the existing constraints and the constraints existing in the SDC file. In case of a conflict, the new constraint has priority over the existing constraint.

The Keep Existing Constraints option is **On** by default. With this option **On**, your timing constraints from the imported SDC files are merged with the existing constraints. When this option is **Off**, all the existing timing constraints are replaced by the constraints in the newly imported SDC files.

## **Keep Existing Physical Constraints**

The Keep Existing Physical Constraints option in the Import Source Files dialog box enables you to merge or replace existing constraints when you import new or modified GCF or PDC files.

Select **Keep existing physical constraints** to preserve all existing physical constraints that you have entered either using one of the MVN tools (ChipPlanner, PinEditor, or the I/O Attribute Editor) or a previous GCF or PDC file. The software will resolve any conflicts between new and existing physical constraints and display the appropriate message.

The Keep Existing Constraints option is **Off** by default. When this option is **Off**, all the physical constraints in the newly imported GCF or PDC files are used. All pre-existing constraints are lost. When this option is **On**, the physical constraints from the newly imported GCF or PDC files are merged with the existing constraints.

## **Compiling Your Design**

After you import your netlist files and select your device, you must compile your design. Compile contains a variety of functions that perform legality checking and basic netlist optimization. Compile checks for netlist errors (bad connections and fan-out problems), removes unused logic (gobbling), and combines functions to reduce logic count and improve performance. Compile also verifies that the design fits into the selected device.

### There are three ways to select the compile command:

In the Tools menu, select Compile.

Click the **Compile** button in the Design Flow.

Click the Compile icon in the toolbar.

If you have not already done so, Designer's Device Selection Wizard prompts you to set the device and package.

During compile, the message window in the Main window displays information about your design, including warnings and errors. Designer issues warnings when your design violates recommended Actel design rules. Actel recommends that you address all warnings, if possible, by modifying your design before you continue.

If the design fails to compile due to errors in your input files (netlist, constraints, etc.), you must modify the design to remove the errors. You must then re-import and re-compile the files.

After you compile the design, you can run Layout to place-and-route the design or use the User Tools (PinEditor, ChipEditor, ChipPlanner, Timer, SmartPower, or NetlistViewer) to perform additional optimization prior to place-and-route.

## **Setting Compile Options**

#### To set compile options

- 1. From the Options menu, click Compile. The Compile Options dialog box opens. The Options available are family specific.

- 2. Select your options, and click **OK**.

Note: ProASIC3/E Compile options appear by default each time you compile the design. If you have disabled this feature, you can click the Options menu and choose Compile to review/change/reset your Compile options.

Compile options vary according to family:

MX, SX, SX-A, eX

**Axcelerator**

ProASIC, ProASICPLUS

ProASIC3/E

## MX, SX, SX-A, eX Compile Options

## **Netlist Pin Properties Overwrite Existing Properties**

During the Compile process, Designer checks the netlist properties. If the netlist file specifies a pin assignment for a pin that was also assigned in PinEditor session, there is a conflict. How this conflict is resolved is determined by your selection in this box.

Designer User's Guide

If this option is off, or unchecked, then Designer uses the assignment made in PinEditor, and the assignment in the netlist file for the conflicting pin is ignored. If this option is on, or checked, then Designer uses the assignment in the netlist file for that pin, and the PinEditor assignment is ignored. If you edit pin assignments in PinEditor, this option is automatically set to "off."

### **Fanout Messages**

Use the control slider in the Messages area to control the warning level. Use the control slider to specify the fanout limit that the Compile step checks against. Setting the control slider to '0' informs the system to use the system defaults. Any non-zero value replaces the system default value for the fanout limit with the user-specified value. Typically, this value range is 1 to 24.

This does not adjust the fanout of the design and it has no effect on the netlist. This only adjusts the warning level, by controlling what level of fanout checking you want to be warned about during Compile. Changing this fanout limit option does not invalidate the Compile design state.

## **Axcelerator Compile Options**

### **Combine Registers into I/Os Where Possible**

The Axcelerator, ProASIC3, and ProASIC3E families includes an optional register on the input path, an optional register on the output path, and an optional register on the 3-state control pin. Select the option Combine Registers into I/Os where possible to take advantage of these registers.

### **Abort on PDC Error**

Setting Abort on PDC Error aborts the PDC import when an error is encountered. When this box is checked, the PDC file is either imported fully or the design is left untouched.

## ProASIC and ProASIC Compile Options

### Include RAM and I/O in Spine and Net Regions

This option affects the behavior of the following:

The use\_global constraint

The set\_net\_region constraint

The creation of spines in the MultiView Navigator

Selecting "Include RAM and I/O in Spine and Net Regions" enables you to assign memory and I/O to spine (LocalClock) and net regions.

When this option is checked, Designer will apply the use\_global and set\_net\_region constraints to core cells, memory, and I/O. When unchecked, Designer will apply the use\_global and set\_net\_region constraints to core cells only. For new designs, this box is automatically checked. For designs created with v5.1 or earlier, this option is unchecked by default. If you change this default setting, you must recompile your design.

This option also determines whether memory and I/O are included in a LocalClock region that you create with the ChipPlanner tool. If checked, memory and I/O are included. If not checked, they are excluded.

## **ProASIC3/E Compile Options**

This interface lets you do the following:

Verify Physical Design Constraints

Perform Globals Management

Netlist Optimization

Generate Compile report

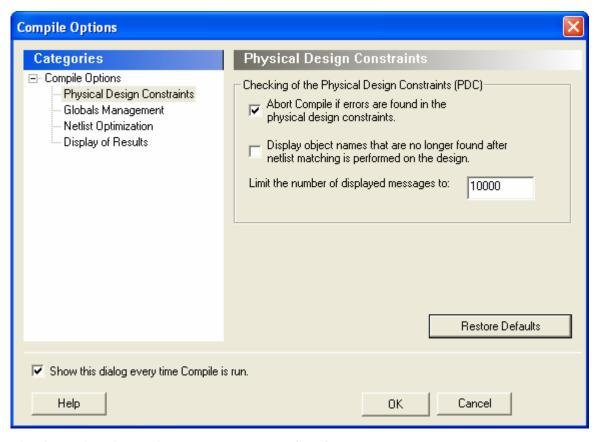

### **Physical Design Constraints**

This interface enables you to verify the Physical Design Constraints (PDC) file.

### **Checking the Physical Design Constraint (PDC)**

**Abort Compile if errors are found in the physical design constraints:** Changes the "Abort on PDC error" behavior. Select this option to stop the flow if any error is reported in reading your PDC file. If you deselect this option, the tool skips errors in reading your PDC file and just reports them as warnings. The default is ON.

**Note:** The flow always stops even if this option is deselected in the following two cases:

If there is a Tcl error (For example, the command does not exist or the syntax of the command is incorrect)

The assign\_local\_clock command for assigning nets to LocalClocks fails. This may happen if any floor planning DRC check fails, such as, region resource check, fix macro check (one of the load on the net is outside the local clock region). If such an error occurs, then the Compile command fails. Correct your PDC file to proceed.

**Note:** Every time you invoke this dialog box, this option is reset to its default value ON. This is to ensure that you have a correct PDC file.

**Display object names that are no longer found after netlist matching is performed on the design:** Displays netlist objects in the PDC that are not found in the imported netlist during the Compile ECO mode. Select this option to report netlist objects not found in the current netlist when reading the internal ECO PDC constraints. The default is OFF.

**Limit the number of displayed messages to:** Defines the maximum number of errors/warnings to be displayed in the case of reading ECO constraints. The default is 10000 messages.

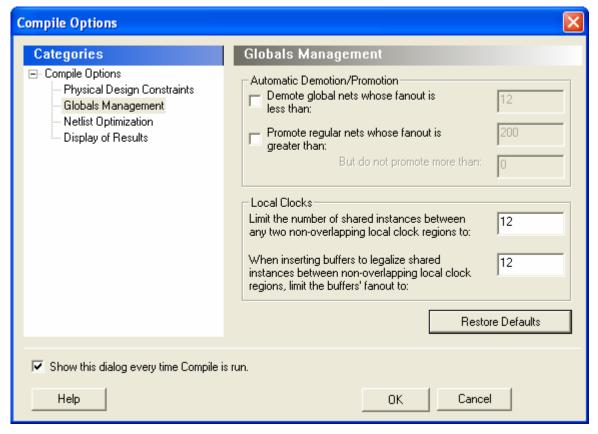

### **Globals Management**

The interface provides a global control to the Compile component of the design flow.

#### **Automatic Demotion/Promotion**

**Demote global nets whose fanout is less than:** Enables the global clock demotion of global nets to regular nets. By default, this option is OFF. The maximum fanout of a demoted net is 12.

**Note:** A global net is not automatically demoted (assuming the option is selected) if the resulting fanout of the demoted net is greater than the max fanout value. Actel recommends that the automatic global demotion only act on small fanout nets. Actel recommends that you drive high fanout nets with a clock network in the design to improve timing and routability.

**Promote regular nets whose fanout is greater than:** Enables global clock promotion of nets to global clock network. By default, this option is OFF. The minimum fanout of a promoted net is 200.

**But do not promote more than:** Defines the maximum number of nets to be automatically promoted to global. The default value is 0. This is not the total number as nets need to satisfy the minimum fanout constraint to be promoted. The promote\_globals\_max\_limit value does not include globals that may have come from either the netlist or PDC file (quadrant clock assignment or global promotion)

**Note:** Demotion of globals through PDC or Compile is done before automatic global promotion is done.

You may exceed the number of globals present in the device if you have nets already assigned to globals or quadrants from the netlist or by using a PDC file. The automatic global promotion adds globals on what already exists in the design.

#### **Local clocks**

Limit the number of shared instances between any two non-overlapping local clock regions to: Defines the maximum number of shared instances allowed to perform the legalization. It is also for quadrant clocks.

The maximum number of instances allowed to be shared by 2 local clock nets assigned to disjoint regions to perform the legalization (default is 12, range is 0-1000). If the number of shared instances is set to 0, no legalization is performed.

When inserting buffers to legalize shared instances between non-overlapping local clock regions, limit the buffers' fanout to: Defines the maximum fanout value used during buffer insertion for clock legalization. Set the value to 0 to disable this option and prevent legalization (default value is 12, range is 0-1000). If the value is set to 0, no buffer insertion is performed. If the value is set to 1, there will be one buffer inserted per pin.

Note: If you assign quadrant clock to nets using MultiView Navigator, no legalization is performed.

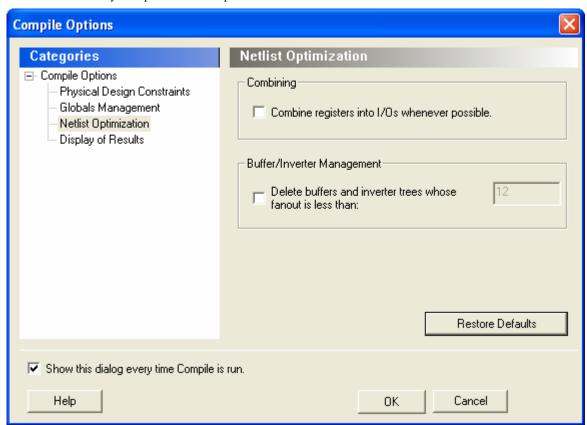

### **Netlist Optimization**

This interface allows you to perform netlist optimization.

### **Combining**

**Combine registers into I/O wherever possible:** Combines registers at the I/O into I/O-Registers. Select this option for optimization to take effect. By default, this option is OFF.

#### **Buffer/Inverter Management**

**Delete buffers and inverter trees whose fanout is less than:** Enables buffer tree deletion on the global signals from the netlist. The buffer and inverter are deleted. By default, this option is OFF. The maximum fanout of a net after buffer tree deletion is 12.

**Note:** A net does not automatically remove its buffer tree (assuming the option is on) if the resulting fanout of the net (if the buffer tree was removed) is greater than the max fanout value. It is recommended that the automatic buffer tree deletion should only act on small fanout nets. From a routability and timing point of view, it is not recommended to have high fanout nets not driven by a clock network in the design.

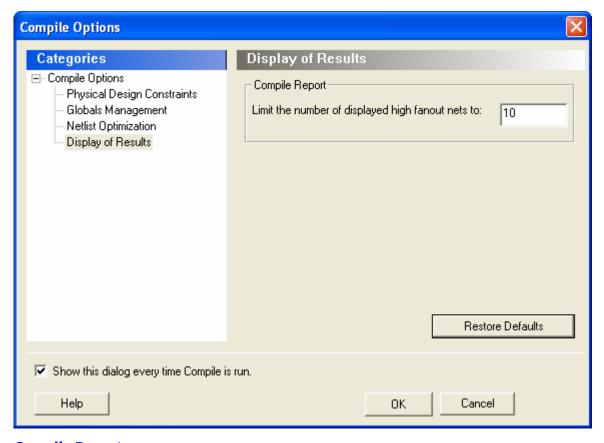

# **Display of Results**

This interface lets you generate a Compile report.

### **Compile Report**

**Limit the number of displayed high fanout nets to:** Enables flip-flop net sections in the compile report and defines the number of nets to be displayed in the high fanout. The default value is 10

# **About Design Constraints**

Design constraints are specifications for placing, implementing, naming, and timing considerations of physical and logical assignments. They are usually either restrictions or properties in your design. There are several types of constraints: routing, timing, area, mapping, and placement constraints.

Timing constraints

ocation and region assignment constraintsLocation and region assignment constraints (placing and routing)

I/O assignment constraints (pin location and I/O attributes)

Attributes

You use constraints to ensure that a design meets timing performance and required pin assignments.

Designer supports both physical and timing constraints. You can set constraints by either using Actel's interactive tools or by importing constraint files directly into Designer.

# **About Location and Region Assignments**

You can set constraints for locations and regions using the ChipPlanner or ChipEditor tool as well as via constraint files.

The tool you use depends on which product family you are designing for:

For ProASIC3E, ProASIC3, ProASIC PLUS, Axcelerator, and ProASIC devices, use ChipPlanner.

For other design families, use ChipEditor.

If you choose to use constraint files to set your location and region assignments, the exact constraint file you use depends on your device family. See Types of physical constraints for more information.

When you open your design (.adb) file, Designer automatically presents you with the appropriate tools in the Design Flow window.

# **About Physical Constraints and Attributes**

## **Physical Constraints**

Physical constraints are the placement and routing constraints that apply to a specific architecture and device. You can either import a constraint file or enter them in your design using one of several tools.

If you are designing for the ProASIC3E, ProASIC3, ProASIC PLUS, Axcelerator, and ProASIC families, you will use the tools available from within the MultiView Navigator. These tools are:

ChipPlanner - Sets location and region assignments

PinEditor in MVN - Sets the pin location constraints

I/O Attribute Editor - Sets I/O attributes

For all other families, you will use the standalone versions of the following tools:

ChipEditor - Sets location and region assignments

PinEditor - Sets I/O attributes and pin location constraints

Physical constraints may also be specified in three types of files. The supported file types depend on the family. See Types of physical constraints for more information.

## **Attributes**

Attributes are the characteristics of logic macros or nets in your design. They indicate placement, implementation, naming, directionality, and other characteristics. This information is used by the design implementation software during placement and routing of a design.

Input and output attributes are described in the documentation for the I/O Attribute Editor. Attributes applicable to a specific tool are described in the documentation for that tool.

# **Types of Physical Constraints**

Designer supports three types of physical constraints:

I/O assignments

Location and region assignments

Clock assignments

### I/O Assignments

Use PinEditor to manually place and configure your I/Os. Or, assign I/O locations automatically by importing one of the following constraint files into Designer:

GCF (ProASIC PLUS and ProASIC families)

PDC (ProASIC3E, ProASIC3, and Axcelerator families)

PIN (all families except ProASIC3E, ProASIC3, ProASIC PLUS, Axcelerator, and ProASIC)

## **Location and Region Assignments**

Use ChipPlanner to view the placement and routing for ProASIC3E, ProASIC3, Axcelerator, ProASIC, and ProASICPLUS designs. Use ChipEditor to view and manually change location assignments for other design families.

You can also assign location constraints and enter region constraints by importing one of the following constraint files into Designer:

GCF (ProASIC and ProASIC PLUS families)

PDC (ProASIC3E, ProASIC3, and Axcelerator families)

## **Clock Assignments**

Use ChipPlanner to assign nets to local clocks in ProASIC and ProASIC PLUS.

You can also assign nets to local clocks and global clocks (with the exception noted below) by importing the following constraint files into Designer:

GCF (ProASIC and ProASIC PLUS families)

PDC (ProASIC3/E and Axcelerator families)

Note: You cannot assign global clocks for Axcelerator.

# **Timing Constraints**

Timing constraints can be entered using the interactive Timer tool or by importing a constraint file.

| Constraint File Type | Supported Families                                 |

|----------------------|----------------------------------------------------|

| SDC                  | Axcelerator, ProASICPLUS, ProASIC3/E, SX-A, and eX |

| DCF                  | SX, SX-A, MX, eX, ACT1, ACT2, and ACT3             |

| GCF                  | ProASIC ONLY                                       |

To understand the complexity of a design and its performance, perform place-and-route with no constraints to see if routing can complete without constraints. If routing completes successfully, you can open Timer to see if the physical design meets timing requirements.

**ProASIC only:** If you are using a synthesis tool such as Synopsys Design Compiler, Actel recommends that you use it to generate a forward SDF file containing path constraints only.

Over constraining a design may result in increased place-and-route run times, while not improving design performance.

# **Running Layout**

Use Layout to place and route your design.

#### To run Layout:

1. Click the Layout button in the Design Flow Window.

2. Layout Options. Select your Layout options and Click OK. Layout options are family specific.

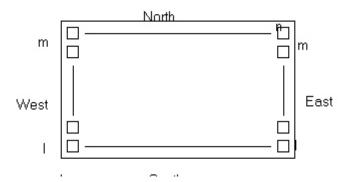

# **Axcelerator Layout Options**

When <u>running Layout</u>, use the Layout Options dialog box to set your Layout options.

### **Timing-driven**

Select this option to run timing-driven Layout. The primary goal of timing-driven layout is to meet <u>timing constraints</u>, with a secondary goal of producing high performance for the rest of the design. Timing-driven Layout is more precise and typically results in higher performance.

Standard layout is selected when the Timing-driven checkbox is unchecked. Standard layout maximizes the average performance for all paths. Each part of a design is treated equally for performance optimization. Standard layout uses net weighting (or criticality) to influence the results. Delay constraints that have been set for a design during place-and-route are not considered, however a delay report based on delay constraints entered in Timer can still be generated for the design. This is helpful to determine if timing-driven Layout is required.

#### **Run Place**

Select this option to run the placer during Layout. If you have not run Layout before, Run Place is checked by default. If your design has already been placed but not routed, this box is not checked. You can also select the following incremental placement options.

**Incrementally**: Select to use previous placement data as the initial placement for the next placement run.

Lock Existing Placement (fix): Select to use and lock previous placement data for the next incremental placement run.

#### **Effort Level**

Use the Effort Level slider to increase the effort Layout uses to place and route your design. The range is 1 to 5 with a default of 3. A higher level of effort generally improves the quality of results, but runs longer.

#### **Run Route**

Select to run the router during Layout. By default, it reflects the current Layout state. If you have not run Layout before, Run Route is checked. Run Route is also checked if your previous Layout run completed with routing failures. If your design has been routed successfully, this box is checked.

Incremental routing is available for Axcelerator devices. When activated, the option sets the previous routing information as the initial starting point. To use the incremental routing option in the script mode, see the <u>Advanced Tcl Layout options for Axcelerator</u> (in the Tcl Scripting section).

### **Use Multiple Passes**

Select to run layout multiple times with different placement seeds. Multiple Pass Layout attempts to improve layout quality by selecting from a greater number of layout results. Click **Configure** to set your <u>Multiple Pass Configuration</u>.

Note: To run Multiple Passes, you must check both Run Place and Run Route.

# ProASIC3/E, ProASICPLUS, and ProASIC Layout Options

When running layout, use the Layout Options dialog box to set your layout options.

### **Timing-Driven**

Select this option to run timing-driven Layout. The primary goal of timing-driven layout is to meet <u>timing constraints</u>, with a secondary goal of producing high performance for the rest of the design. Timing-driven Layout is more precise and typically results in higher performance.

When not checked, standard layout runs. Standard layout maximizes the average performance for all paths. Each part of a design is treated equally for performance optimization. Standard layout uses net weighting (or criticality) to influence the results. Delay constraints that have been set for a design during place-and-route are not considered, however a delay report based on delay constraints entered in Timer can still be generated for the design. This is helpful to determine if timing-driven Layout is required.

#### **Run Place**

Select this option to run the placer during Layout. By default, it reflects the current Layout state. If you have not run Layout before, Run Place is checked by default. If your design has already been placed but not routed, this box is not checked by default. You can also select the following incremental placement options.

Incrementally: Select to use previous placement data as the initial placement for the next place run.

Lock Existing Placement (fix): Select to preserve previous placement data during the next incremental placement run.

#### **Run Route**

Select to run the router during Layout. By default, it reflects the current Layout state. If you have not run Layout before, Run Route is checked. Run Route is also checked if your previous Layout run completed with routing failures. If your design has been routed successfully, this box is checked.

**Incrementally**: Select to fully route a design when some nets failed to route during a previous run. You can also use it when the incoming netlist has undergone an E.C.O. (Engineering Change Order). Incremental routing should only be used if a low number of nets fail to route (less than 50 open nets or shorted segments). A high number of failures usually indicates a less than optimal placement (if using manual placement through macros, for example) or a design that is highly connected and does not fit in the device. If a high number of nets fail, relax constraints, remove tight placement constraints, or select a bigger device and rerun routing.

### **Use Multiple Passes**

Select to run layout multiple times with different seeds. Multiple Pass Layout attempts to improve layout quality by selecting from a greater number of layout results. Click **Configure** to set your <u>Multiple Pass Configuration</u>.

Click the **Advanced** button to set Timing-Driven options.

# ProASIC3/E, ProASICPLUS, and ProASIC Layout Advanced Options

To set these advanced options during Layout, click the Advanced button in the Layout dialog box.

### **Placer Timing Weight**

Setting this option to values within a recommended range of 1-4 changes the weight of the timing objective function, thus influencing the results of timing-driven place-and-route in favor of either routability or performance. This option is available only when timing constraints have been defined.

**Note:** If you change the Timing Weight you must re-run the placer to complete routing. Changing the Timing weight has no effect if you do not re-run the placer.

#### **Restore Defaults**

Click **Restore Defaults** to run the factory default settings for advanced options.

# eX, SX, SX-A Layout Options

When running layout, use the Layout dialog box to set your layout options.

### **Timing-Driven**

Select to run Timing-Driven Layout. The primary goal of Timing-Driven layout is to meet <u>timing constraints</u>, while still producing high performance for the rest of the design. Timing-Driven Layout is more precise and typically results in higher performance. This option is available only when timing constraints have been defined.

When not checked, standard layout runs. Standard layout maximizes the average performance for all paths. Each part of a design is treated equally for performance optimization. Standard layout uses net weighting (or criticality) to influence the results. Delay constraints that have been set for a design during place-and-route are not considered, however a delay report based on delay constraints entered in Timer can still be generated for the design. This is helpful to determine if Timing-Driven Layout is required.

### **Place Incrementally**

Select to use previous placement data as the initial placement for the next place run.

Lock Existing Placement: Select to preserve previous placement data during the next incremental placement run.

### **Use Multiple Passes (eX and SX-A only)**

Select to run layout multiple times with different seeds. Multiple Pass Layout attempts to improve layout quality by selecting from a greater number of layout results. Click **Configure** to set your <u>Multiple Pass Configuration</u>.

#### **Advanced**

Click the Advanced button to set Extended Run and Timing-Driven options.

# eX, SX, and SX-A Advanced Layout Options

To set these advanced options during Layout, click the Advanced button in the Layout dialog box.

#### **Extended Run**

Select this to run a greater number of iterations during optimization within a single layout pass. An extended run layout can take up to 5 times as long as a normal layout.

#### **Effort Level**

This setting specifies the duration of the timing-driven phase of optimization during timing-driven Layout. Its value specifies the duration of this phase as a percentage of the default duration. This option is available only when timing constraints have been defined

The default value is 100 and the selectable range is within 25 - 500. Reducing the effort level also reduces the run time of timing-driven place-and-route (TDPR). With an effort level of 25, TDPR is almost four times faster. With fewer iterations, however, performance may suffer. Routability may or may not be affected. With an effort level of 200, TDPR is almost two times slower. This variable does not have much effect on timing.

#### **Timing Weight**

Setting this option to values within a recommended range of 10-150 changes the weight of the timing objective function, thus influencing the results of timing-driven place-and-route in favor of either routability or performance. This option is available only when timing constraints have been defined

The timing weight value specifies this weight as a percentage of the default weight (i.e. a value of 100 has no effect). If you use a value less than 100, more emphasis is placed on routability and less on performance. Such a setting would be appropriate for a design that fails to route with TDPR. In case more emphasis on performance is desired, set this variable to a value higher than 100. In this case, routing failure is more likely. A very high timing value weight could also distort the optimization process and degrade performance. A value greater than 150 is not recommended.

#### **Restore Defaults**

Click Restore Defaults to run the factory default settings for advanced options.

# ACT, MX, and DX Layout Options

### **Timing-Driven**

Select this option to run Timing-Driven Layout. The primary goal of timing-driven layout is to meet <u>timing constraints</u>, with a secondary goal of producing high performance for the rest of the design. timing-driven Layout is more precise and typically results in higher performance. This option is available only when timing constraints have been defined.

When not checked, standard layout runs. Standard layout maximizes the average performance for all paths. Each part of a design is treated equally for performance optimization. Standard layout uses net weighting (or criticality) to influence the results. Delay constraints that have been set for a design during place-and-route are not considered, however a delay report based on delay constraints entered in Timer can still be generated for the design. This is helpful to determine if Timing-Drive Layout is required.

### **Place Incrementally**

Select to use previous placement data as the initial placement for the next place run.

Lock Existing Placement: Select to preserve previous placement data during the next incremental placement run.

#### Advanced

Click **Advanced** to set Extended Run options.

# ACT, MX, and DX Advanced Layout Options

To set these advanced options during Layout, click the Advanced button in the Layout dialog box.

#### **Extended Run**

Select this to run a greater number of iterations during optimization. An extended run layout can take up to 5 times as long as a normal layout.

#### **Restore Default**

Click **Restore Defaults** to run the factory default settings for advanced options.

# **Incremental Placement**